**CHALMERS**

UNIVERSITY OF TECHNOLOGY

# 2020-01-30 Technical information

## Christian Križan

Research engineer, QTL

[križan@chalmers.se](mailto:križan@chalmers.se)

- **Upcoming specs, clarifications**

- **Ethernet interfacing**

- **Questions and their answers**

# Specification documents incoming

- Hints on testing

- Tips for concepts to research

- Prioritisation

- Articles for various modules, sinusoidal generation

- (Maybe?) Tips and ideas for handling dropped packages

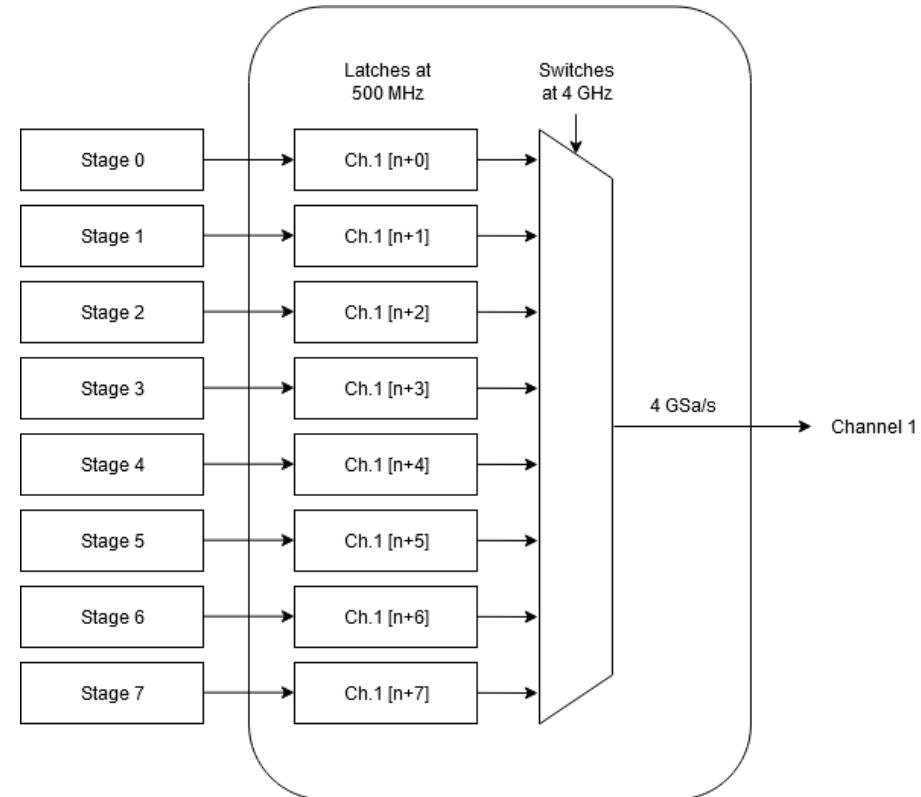

# Clarification on the DAC

# Ethernet interfacing

- The Nexys 4 board carries a PHY chip (LAN8720). Its pin routing to the Artix 7 FPGA is given in the Nexys 4 manual, interfacing details are found in a LAN8720 datasheet.

For this project, we have specified that you interface to this PHY via RMII.

- The resulting bitstream will (hopefully) contain Ethernet frames.

In such a frame there will be a bitlength designated ('by standards') as an IP packet.

- Within that packet, you will find a UDP packet.

- The header of this packet contains the destination port, which you will use to figure out which target DAC FIFO this packet's payload is destined for. The ensuing data (and its format) is given in the module descriptive document in Canvas.

# Cont. payloads

- Everything else that does not conform to the expected stream data, send it to other\_data\_tx. This includes control words.

- These control words will have to be parsed by a control word host. Its output is expected to be routed to various blocks in your overall architecture.

**Question: Would you like a module graphic for this host?**

- OK, but what about ARP?

The ARP request is contained within the IP Datagram field in the previous slide.

# Address Resolution Protocol

- Every node on the network has its own MAC address. But applications communicate using IP addresses. Thus at some level, we must link MAC addresses to IP addresses.

- The ARP request is basically shouting on the network

'Whom has the IP address 003.133.133.13' ?

(... and whom you're supposed to yell the answer to.)

- The guilty node responds to the specific address. All other nodes stay quiet.

In this project, you'll handle this ARP tango in a separate block within the Ethernet communications module.

- Manual MAC to (static) IP linking can be done manually in your OS of choice, but it's a delicate matter.

**Which is the whole point of including this block in this project.**

# Suggested implementation steps

1. Begin by interfacing to the Nexys 4 PHY

2. Dissect a faked payload and fetch its status (UDP or not?)

3. Add discriminator which sends everything in port range 30000 – 30255 onto some data bus

4. Add ARP request block, signal whether an ARP package was detected

5. Try to do everything above in reverse, loopback the data bus, and monitor on the PC using some serial monitoring program (like Wireshark)

6. Add missing functionality, although without AXI

7. Get AXI working, the bus you'll use for all other intra-'big module'-communication

# Answers to questions

# Answers to questions

- Stream ID bus

- The RLE encoding

- Packet sequence numbering

- How to target a DAC channel

- Ethernet data structure

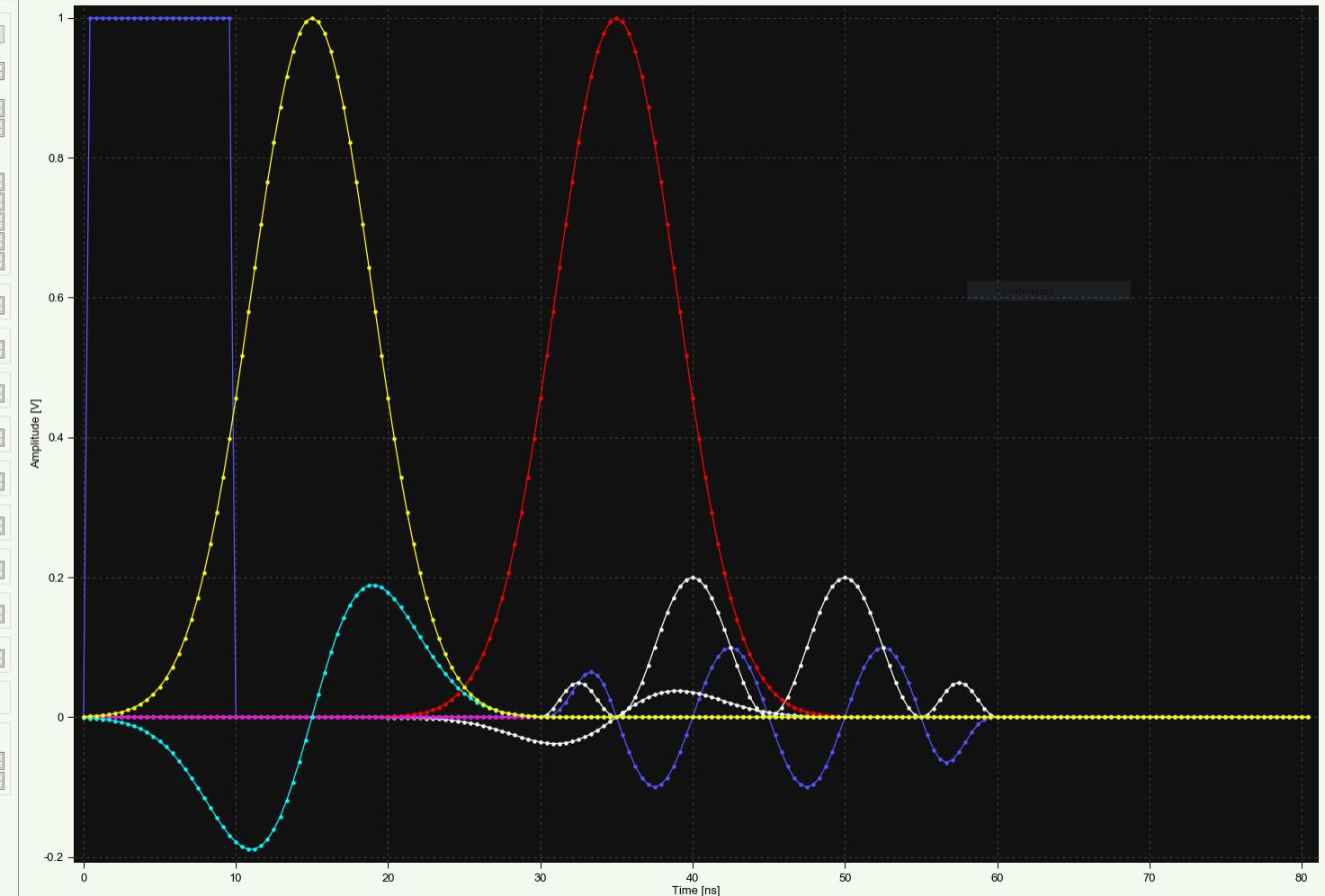

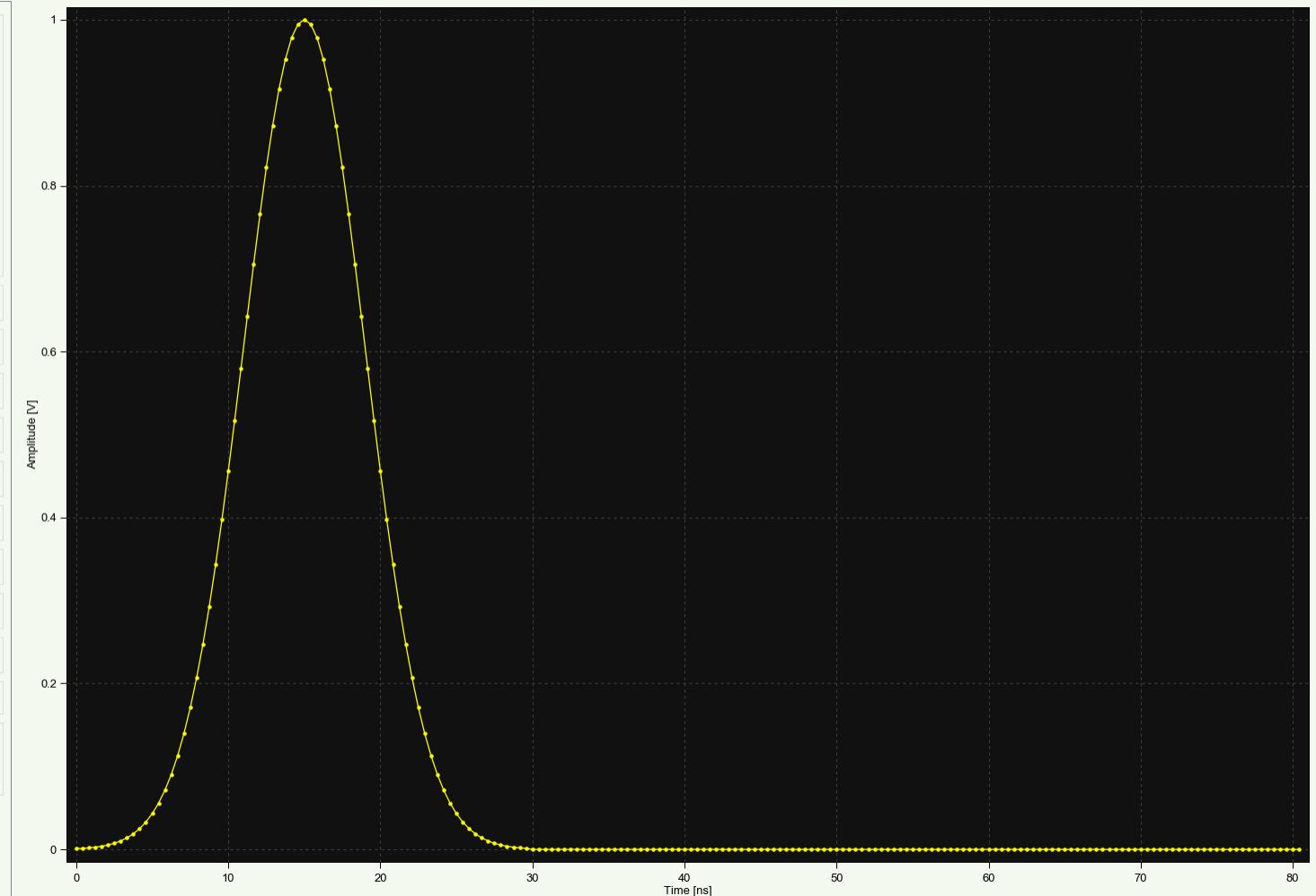

- Windowing

- Sum block

- Research papers for the modules (NCO!)

- Time needed in this project for every module

# “The minimum system”

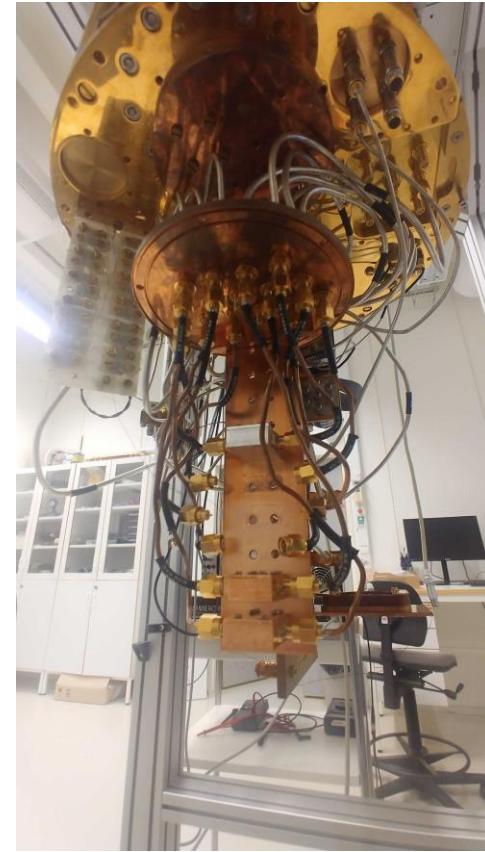

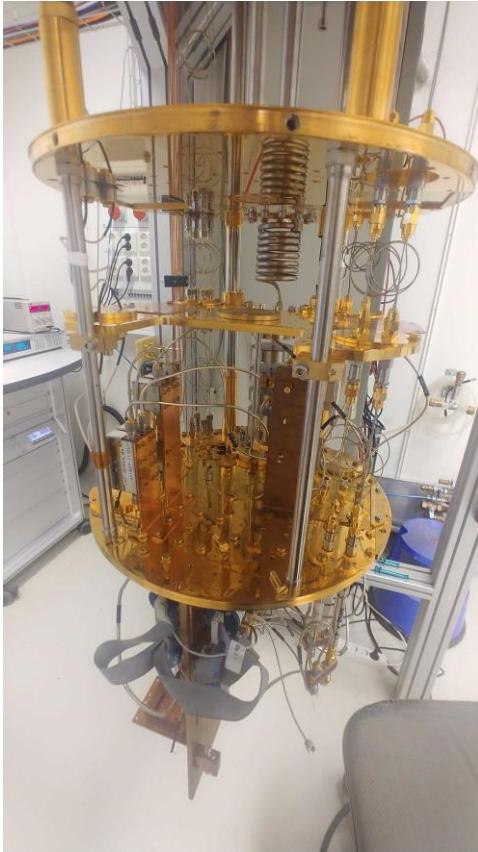

- Ultra-bare minimum that can run on the QPU:

- 1. Ethernet module except ARP functionality.

- 2. Naïve, dumb and slow stream management without DDR. Basically EDF constrained (earliest-deadline-first)

- 3. Two upconversion stages with: FIFO, no RLE (just loose samples...), no IQ mixing ergo no NCO, **BUT a single target upconversion set in the DAC itself**, no summation (has to be done by the PC before-hand (slow)).

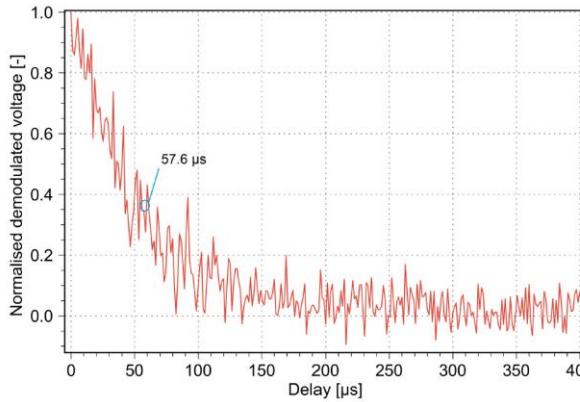

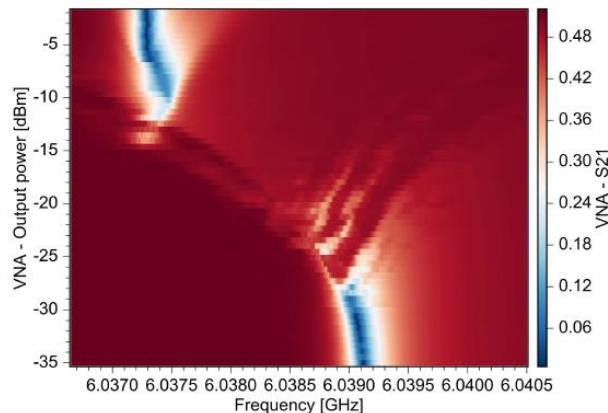

- 4. A single downconversion stage with: no IQ mixing ergo no NCO, **BUT a single target downconversion set in the ADC itself**, no skip/store, but yet a FIFO at the end.

- What can you do with that? Actually quite a lot. More than this was not needed very recently to verify that the qubits you'll be using are working.

- Also, completion of any one of the four major modules yields something that is usable.

# QPU control signalling

Trace: All  Get trace

Sections

- Communication

- Sequence

- Waveform

- 1-QB gates XY

- 1-QB gates Z

- QB spectra

- 2-QB gates

- Tomography

- Predistortion

- Cross-talk

- Readout

- Output

- Demodulation

Readout

Readout pulse type:   Uniform amplitude   Uniform pulse shape   Width [s]:   Duration [s]:   Match main sequence waveform size  Distribute readout phases  Readout delay [s]:   Readout I/Q ratio:   Offset I [V]:   Offset Q [V]:   IQ skew [deg]:   Readout #1 Frequency [Hz]:   Readout #2 Frequency [Hz]:   Readout #3 Frequency [Hz]:   Readout #4 Frequency [Hz]:   Readout #5 Frequency [Hz]:   Readout #6 Frequency [Hz]:   Readout #7 Frequency [Hz]:   Readout #8 Frequency [Hz]:   Readout #9 Frequency [Hz]:   Readout predistortion  Predict readout waveform  Readout trig  Generate readout trig  Readout trig amplitude [V]:   Readout trig duration [s]:

Trace: Trace - II

Get trace Save trace

Sections

Communication

Sequence

Waveform

1-QB gates XY

1-QB gates Z

QB spectra

2-QB gates

Tomography

Predistortion

Cross-talk

Readout

Output

Demodulation

## Readout

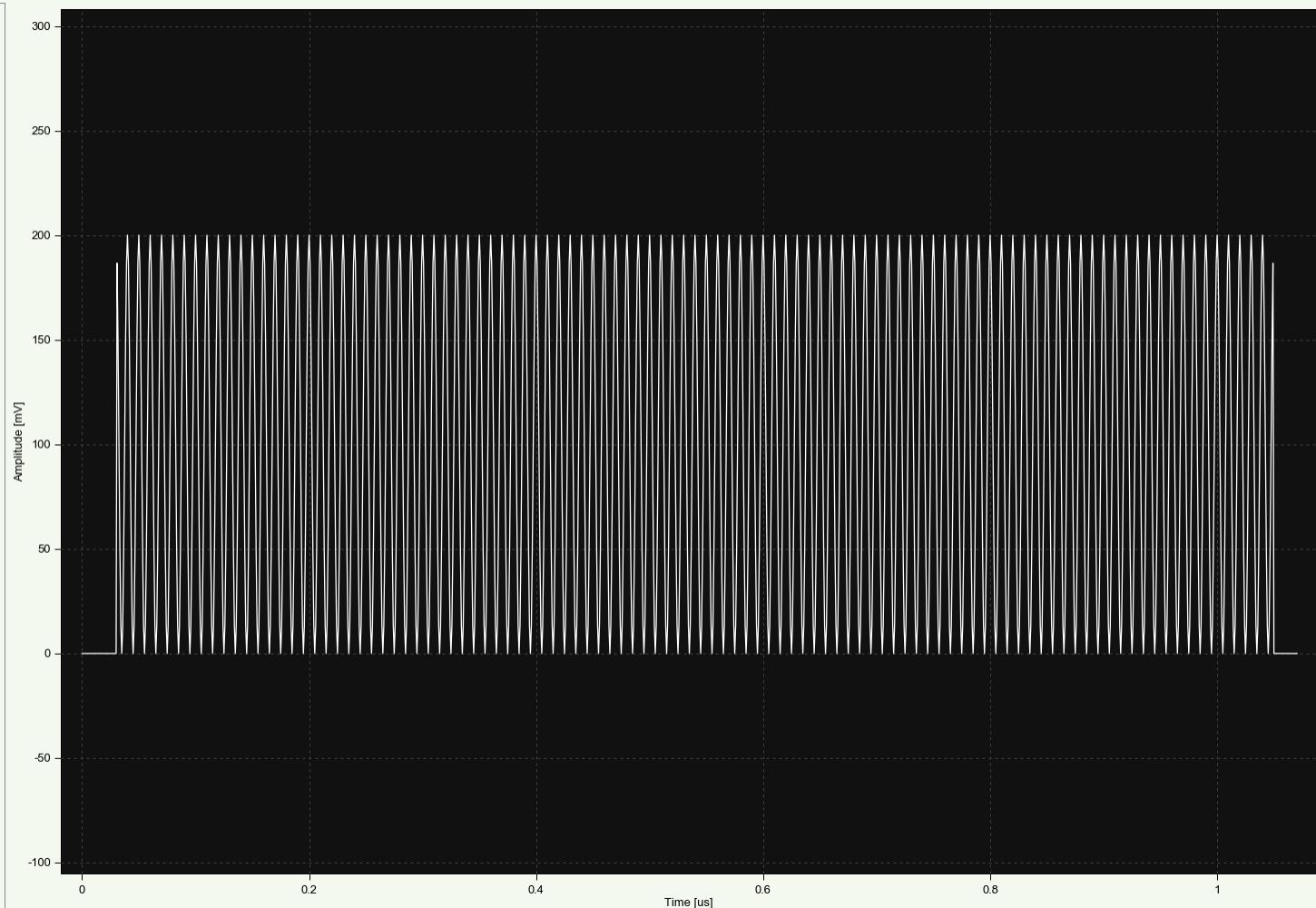

Readout pulse type: Cosine

Uniform amplitude

Amplitude [V]: 100E-3

Uniform pulse shape

Width [s]: 10E-9

Duration [s]: 20E-9

Match main sequence waveform size

Distribute readout phases

Readout delay [s]: 0

Readout I/Q ratio: 1

Offset I [V]: 0

Offset Q [V]: 0

IQ skew [deg]: 0

## Readout #1

Frequency [Hz]: 100E6

## Readout #2

Frequency [Hz]: 0

## Readout #3

Frequency [Hz]: 0

## Readout #4

Frequency [Hz]: 0

## Readout #5

Frequency [Hz]: 0

## Readout #6

Frequency [Hz]: 0

## Readout #7

Frequency [Hz]: 0

## Readout #8

Frequency [Hz]: 0

## Readout #9

Frequency [Hz]: 0

Readout predistortion

Predistort readout waveform

Readout trig

Generate readout trig

Readout trig amplitude [V]: 1

Readout trig duration [s]: 20E-9

# QPU readout

Trace:

Trace - Readout 1

Get trace

Save trace

Sections

Communication

Sequence

Waveform

1-QB gates XY

1-QB gates Z

QB spectra

2-QB gates

Tomography

Predistortion

Cross-talk

Readout

Output

Demodulation

Readout

Readout pulse type:   Uniform amplitude    Uniform pulse shape          Match main sequence waveform size  Distribute readout phases

Readout #1

Readout #2

Readout #3

Readout #4

Readout #5

Readout #6

Readout #7

Readout #8

Readout #9

Readout predistortion  Predistort readout waveform

Readout trig  Generate readout trig

# Visit?

Working on it

# Contract?

# Open-class questions

Or swoosh me a pigeon to [krizan@chalmers.se](mailto:krizan@chalmers.se) or something :)

**CHALMERS**

UNIVERSITY OF TECHNOLOGY