# Introduction to on-chip interconnect

Elmore delay model

Lecture 7 (or really 9) continued

Tuesday October 2, 2018

# Outline

- Elmore delay model – a generalized model

- How to handle wire branches

- Conclusions

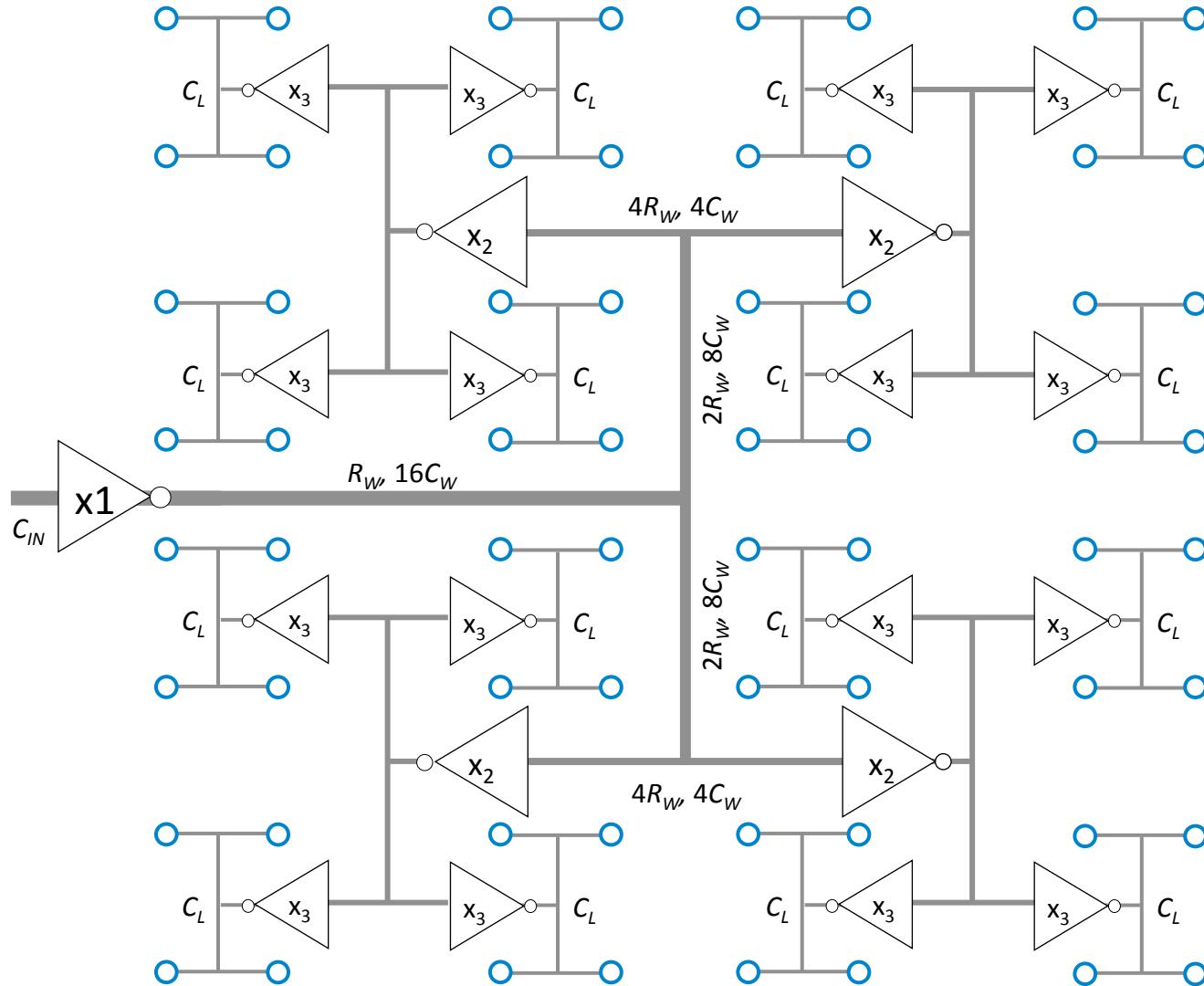

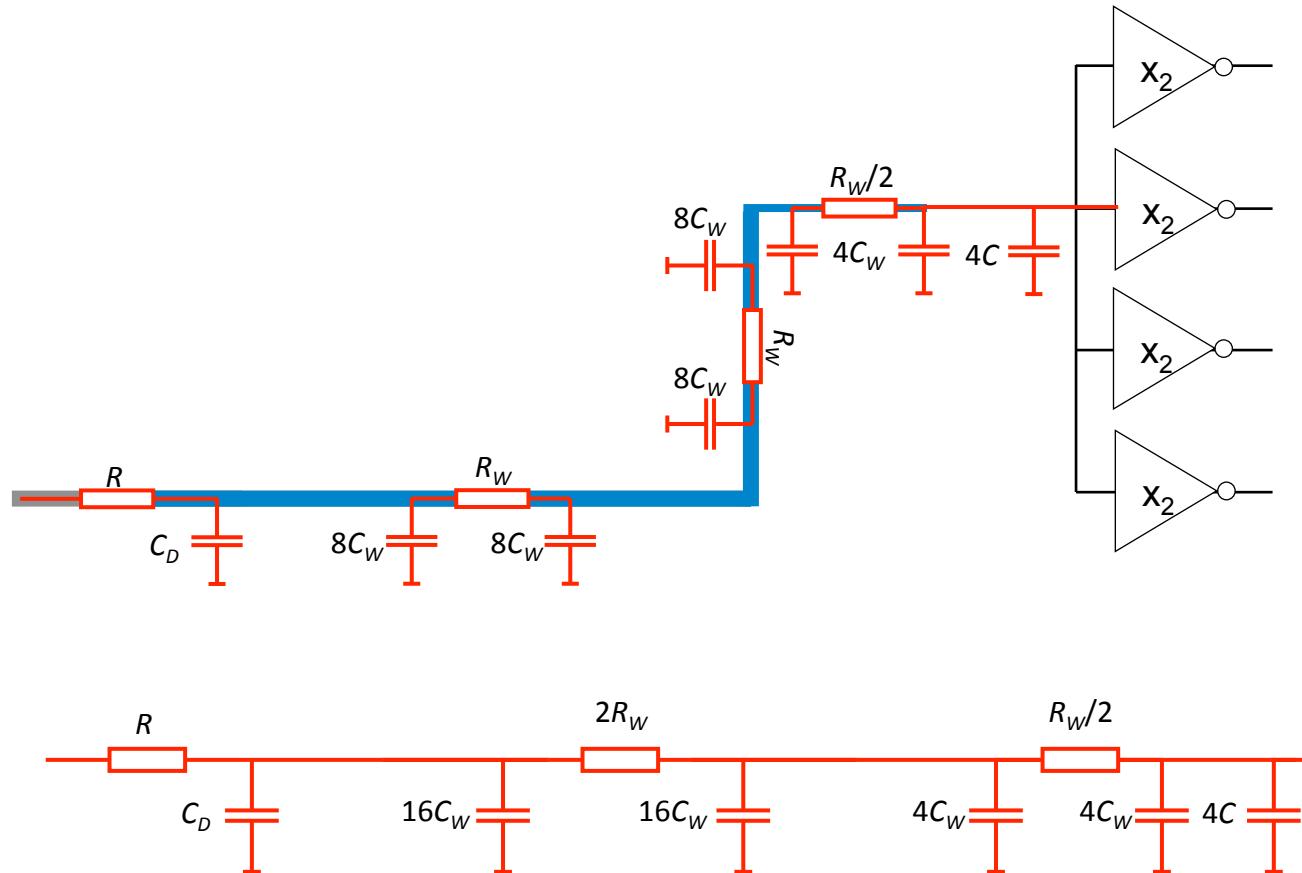

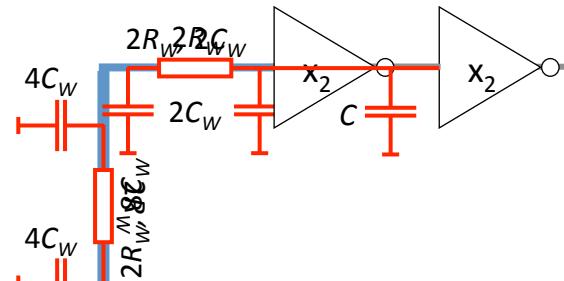

# H-tree clock distribution

# Identify the critical timing path

# Identify the critical timing path

# Identify the critical timing path

# Identify the critical timing path

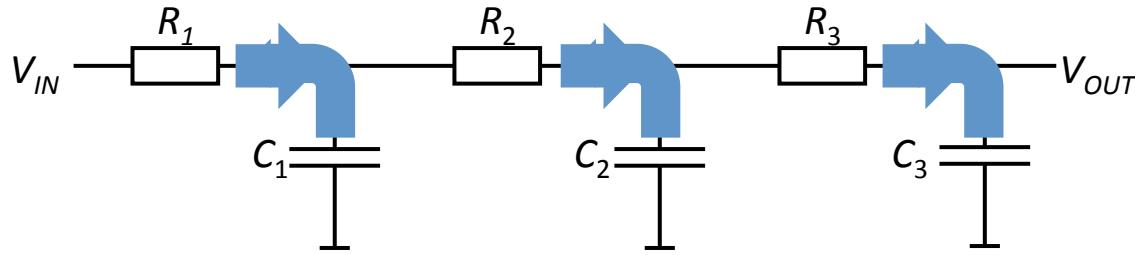

# General solution

Each capacitor is multiplied by its own time constant resistance!

$$T_E = R_B (R_1 + R_2 + R_3) + R_2 (R_2 + R_B) + R_B R_{13}$$

Transfer function

$$H(s) = \frac{1}{as^3 + bs^2 + cs + 1}$$

$$a = R_1 R_2 R_3 C_1 C_2 C_3$$

$$b = R_1 R_2 C_1 C_2 + R_1 R_2 C_1 C_3 + R_1 R_3 C_2 C_3 + R_2 R_3 C_2 C_3$$

$$c = R_1 (C_1 + C_2 + C_3) + R_2 (C_2 + C_3) + R_3 C_3$$

This transfer function corresponds to a third order linear differential equation

The solution is a sum of three exponentials with three different time constants

We cannot solve this analytically.

But if we assume that there is a dominant time constant  $T_E$  it is given by  $c$

$$T_E = R_1 (C_1 + C_2 + C_3) + R_2 (C_2 + C_3) + R_3 C_3$$

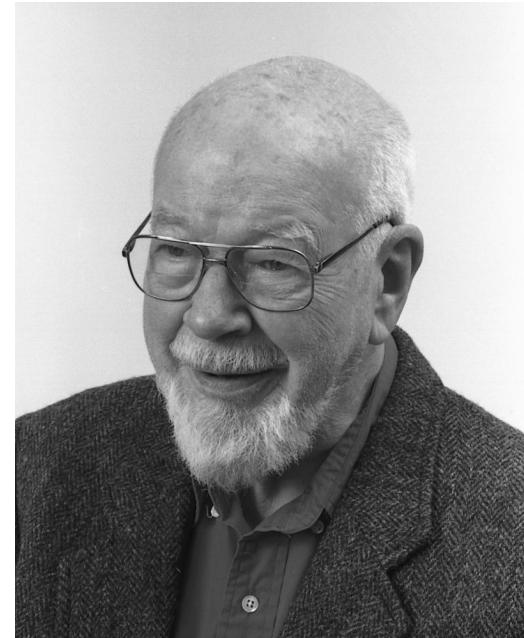

# The man behind Elmore delay

- William Cronk Elmore (1909 - 2003) was an American physicist, educator, and author.

- He is best known for his work on and related to the Manhattan project during World War II.

- Professor of Physics at Swarthmore College, Pennsylvania, from 1938 to 1974.

- Authored two influential books during his life,

- Electronics-Experimental Techniques with M. Sands

- Physics of Waves with Mark Heald.

- He is also known for deriving a simple approximation for the delay through an RC network, known as the Elmore delay.

- Despite his clear potential for advancing theoretical and experimental physics, Elmore was known for developing (and publishing) laboratory experiments that effectively taught students the fundamentals of physics.

W. C. Elmore

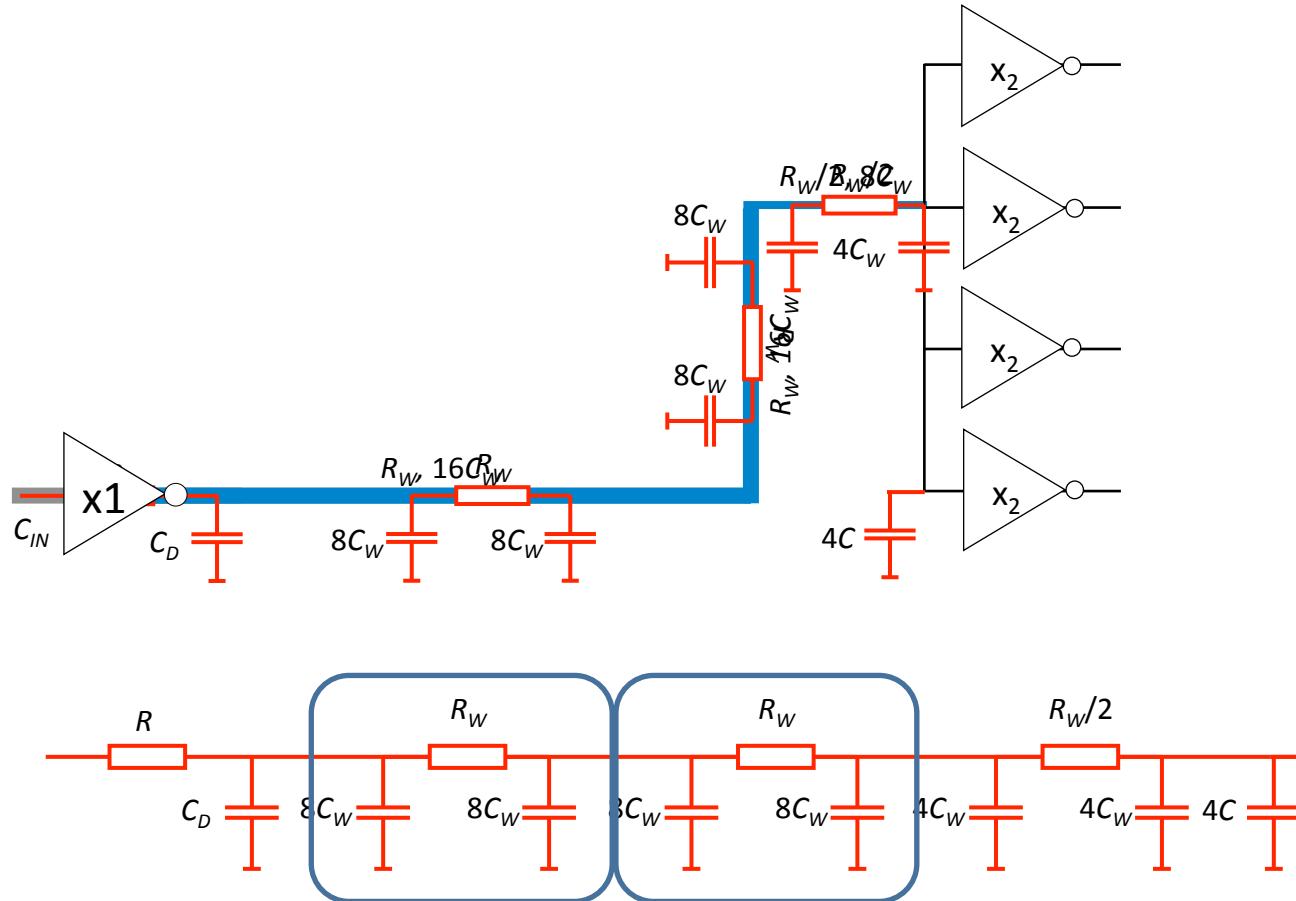

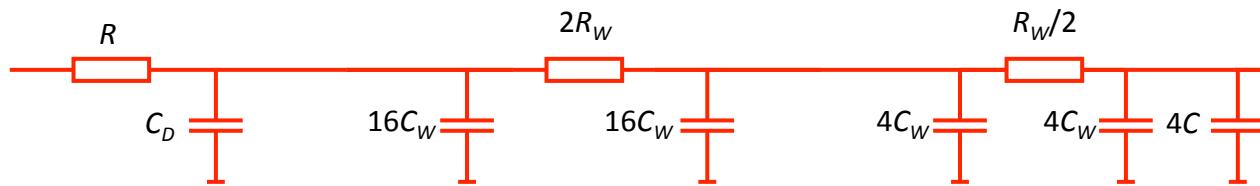

# Identify the critical timing path

$$T_E = R(C_D + 4C) + R \times 40C_W + 2R_W(4C + 24C_W) + \frac{R_W}{2}(4C + 4C_W)$$

$$T_E = R(C_D + 4C) + 40RC_W + 10R_WC + 50R_WC_W$$

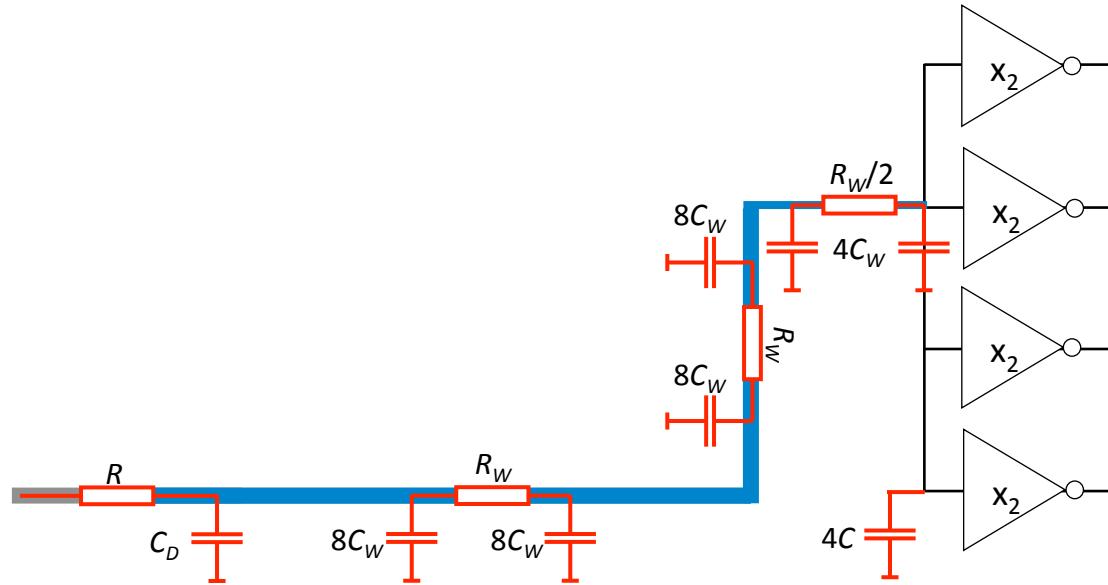

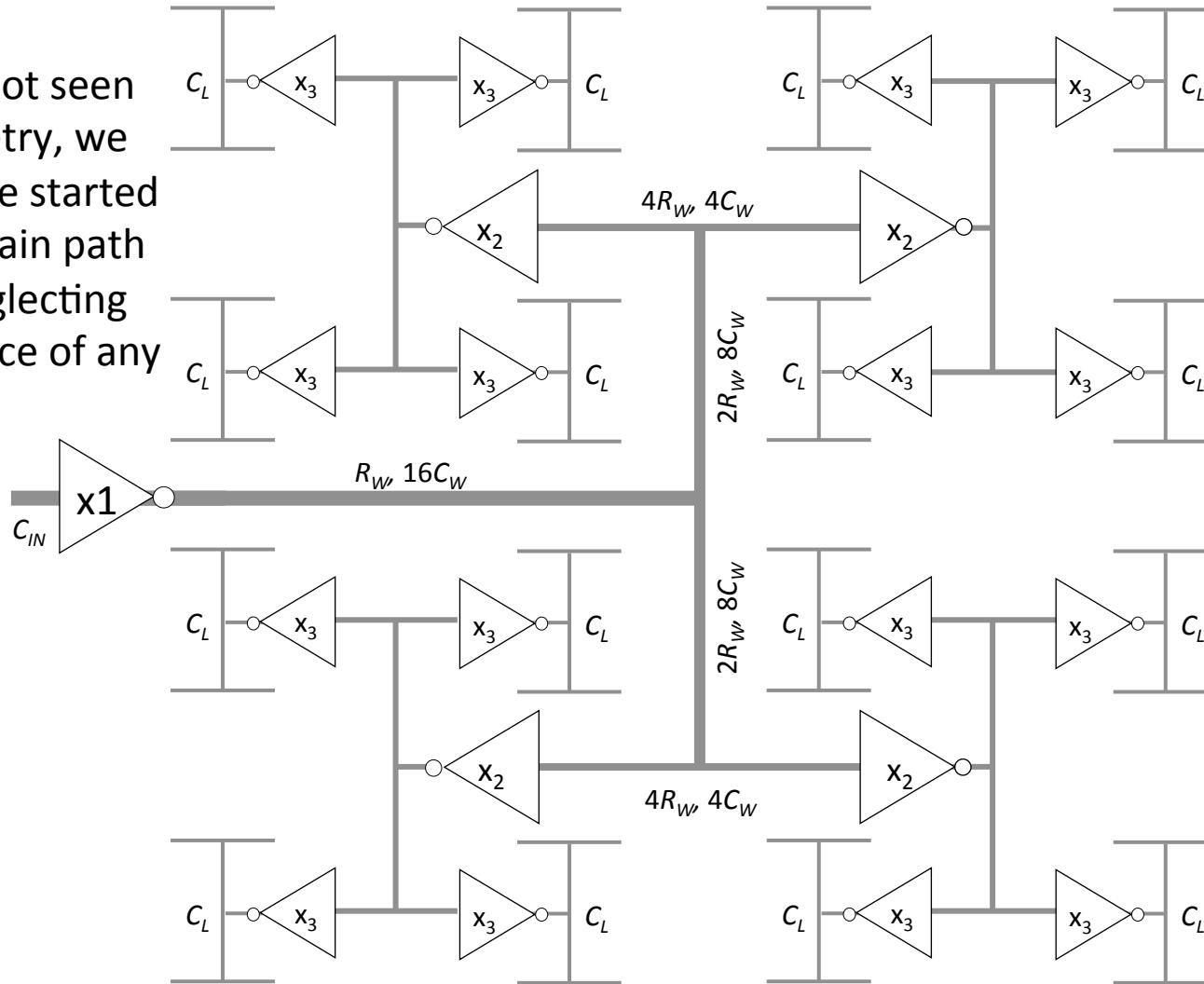

# H-tree clock distribution

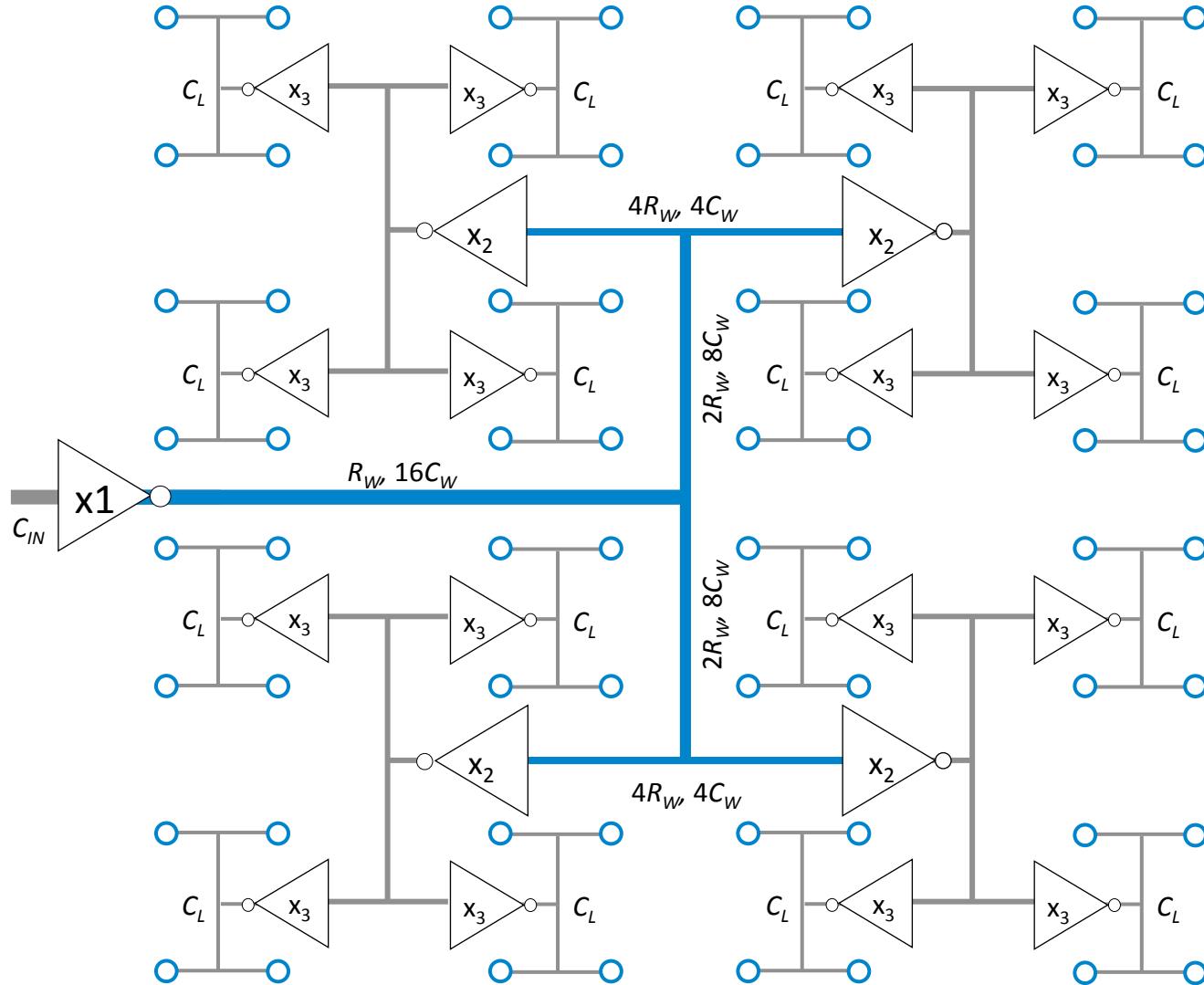

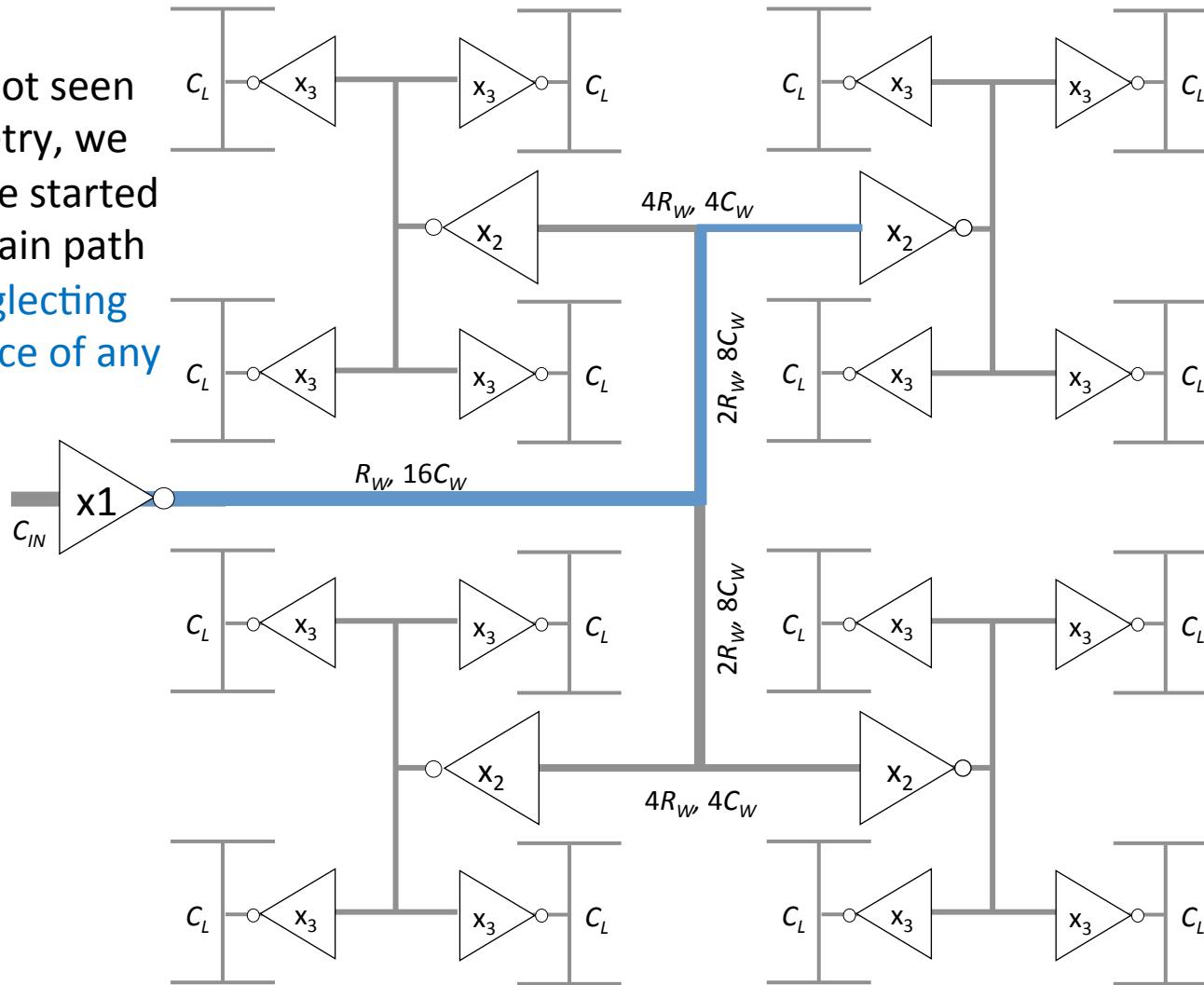

If we had not seen the symmetry, we should have started with the main path delay – neglecting the influence of any branches

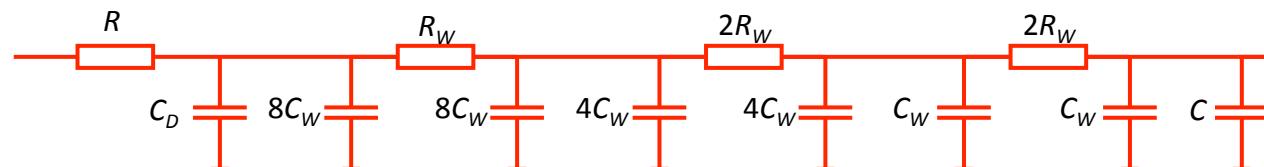

# Always start by identifying main path

If we had not seen the symmetry, we should have started with the main path delay – neglecting the influence of any branches

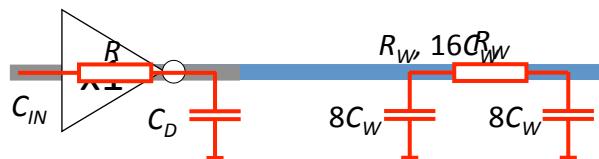

# Always start by identifying main path

If we had not seen the symmetry, we should have started with the main path delay – neglecting the influence of any branches

Electrical RC wire model (neglecting branches)

Obtain Elmore time constant

(by multiplying each resistance by all downstream capacitances)

$$T_{E,main} = R(C_D + C) + R \times 26C_W + R_W(C + 18C_W) + 2R_W(C + 6C_W) + 2R_W(C + C_W)$$

$$T_{E,main} = R(C_D + C) + 26RC_W + 5R_WC + 32R_WC_W$$

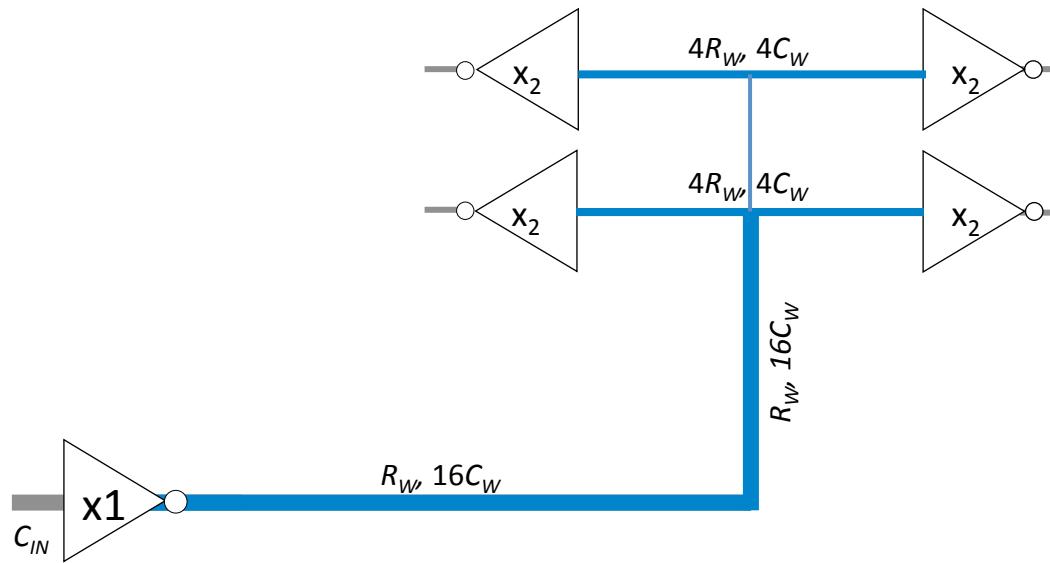

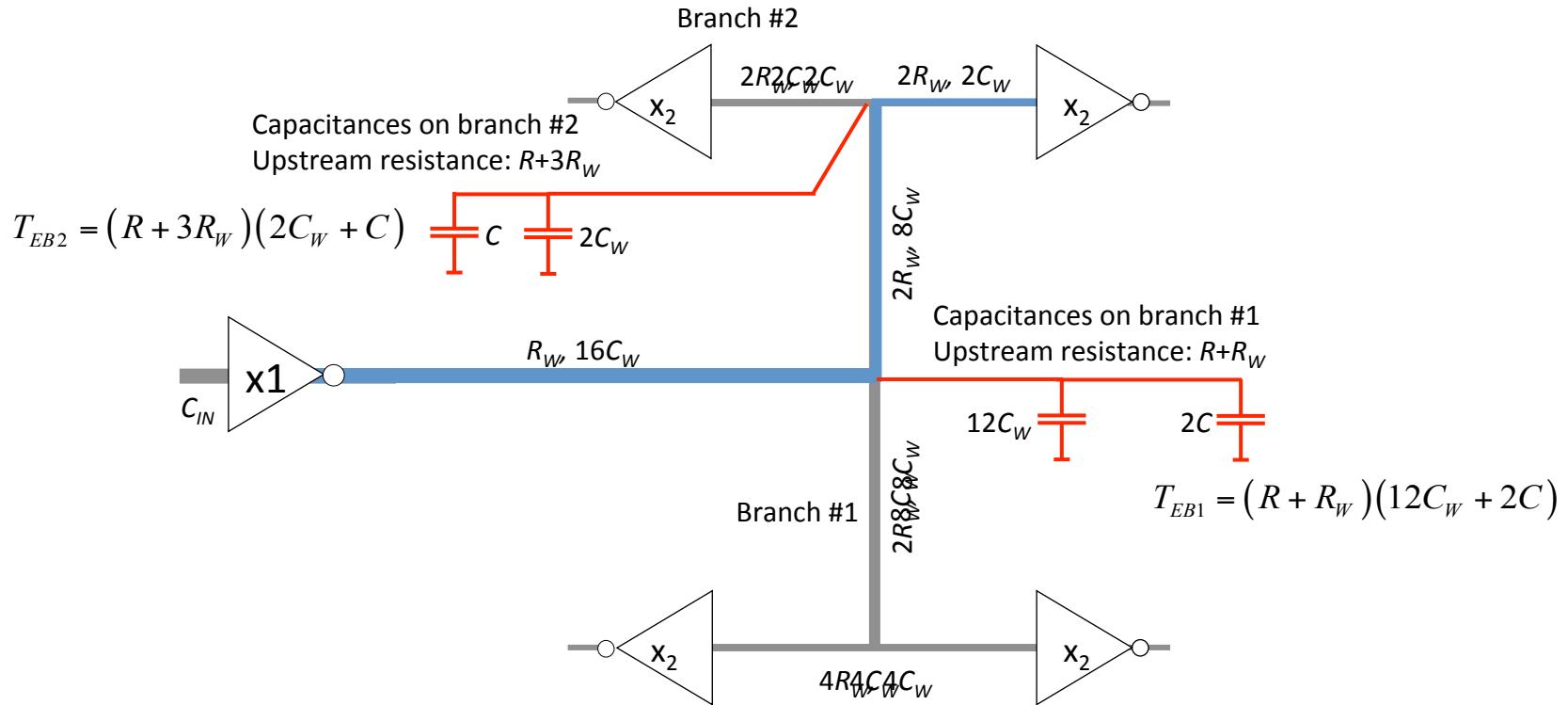

# Then consider neglected branches

We have two neglected branches: #1 and #2

Rule of thumb: Forget about the branch resistances, only consider branch capacitances

Branch contribution to Elmore time constant:  $T_{E,branches} = 3RC + 14RC_w + 5R_wC + 18R_wC_w$

Total Elmore time constant:  $T_E = R(C_D + 4C) + 40RC_w + 10R_wC + 50R_wC_w$

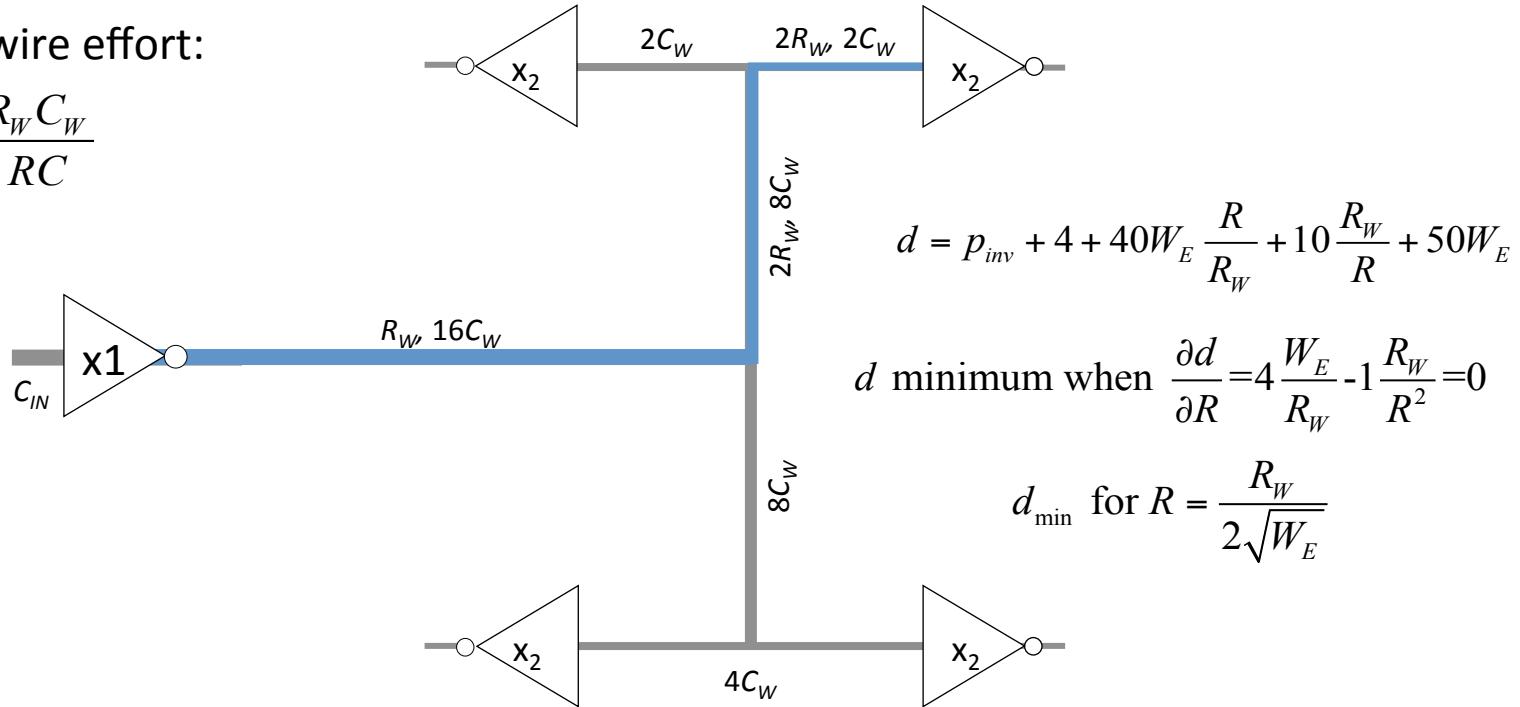

# Inverter sizing

How to size driver inverter to minimize the time constant, and hence the wire delay?

Normalize Elmore time constant:  $d = \frac{T_E}{RC} = p_{inv} + 4 + 40 \frac{R_W C_W}{RC} \frac{R}{R_W} + 10 \frac{R_W}{R} + 50 \frac{R_W C_W}{RC}$

Define wire effort:

$$W_E = \frac{R_W C_W}{RC}$$

$$\text{Total Elmore time constant: } T_E = R(C_D + 4C) + 40RC_W + 10R_W C + 50R_W C_W$$

# Conclusion

We have learnt two things:

- The Elmore model – a generalized delay model

- Relying on the existence of a dominating time constant

- How to handle the influence on delay of branches

- Main timing path first, neglecting branches

- Then consider branches neglecting any branch resistances only considering branch capacitances!

# Thanks a lot for listening!