# Geometric design rules for 65 nm CMOS

## Contact & via rules

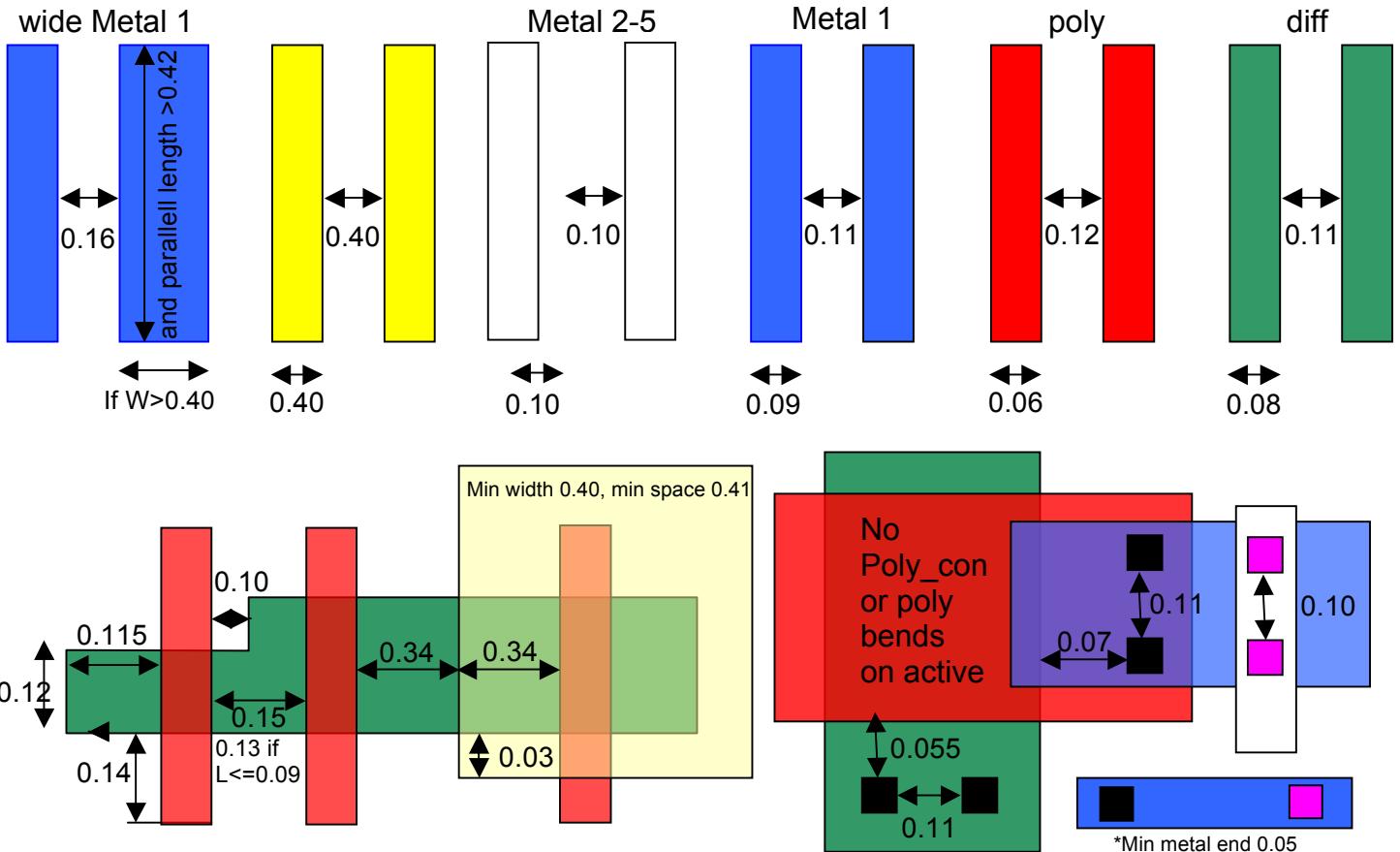

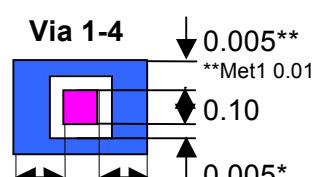

All contact and via sizes are exact measures

\*Two opposite sides at least 0.03 enclosure

\*\*If two opposite metal ends enclose 0.04 then 0.0 OK on remaining

\*\*\*If two opposite poly ends enclose 0.04 then 0.01 OK on remaining

At least two 0.05 metal ends on metal pad

At least two 0.08 metal ends on metal pad

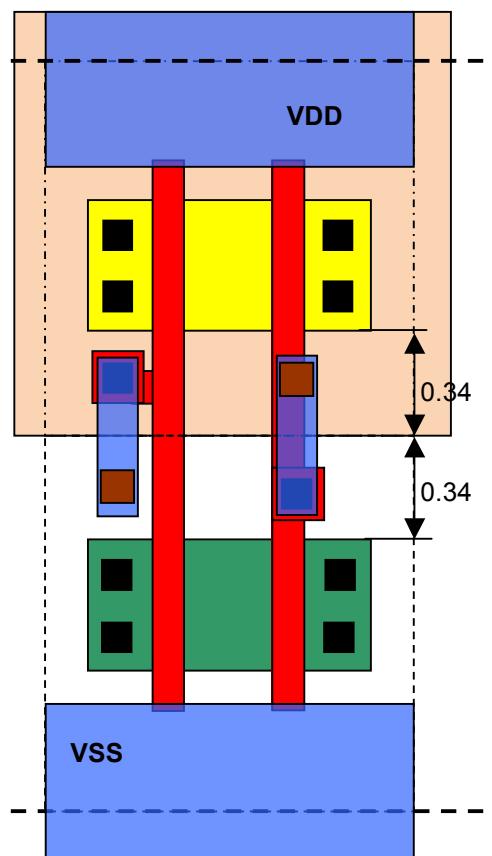

0.34 (min 0.54 in array)

## Standard cell template

with rails, well, pplus and nplus design rules

|                                           |                                                  |           |                                                 |                                               |

|-------------------------------------------|--------------------------------------------------|-----------|-------------------------------------------------|-----------------------------------------------|

| 1. Well                                   |                                                  |           |                                                 |                                               |

| 1.1                                       | Width                                            | 0.47      | 6. Contact to active                            |                                               |

| 1.2                                       | Space (same potential)                           | 0.47      | 6.1                                             | Contact size exactly                          |

|                                           | Space (different potentials)                     | 1.00      | 6.2                                             | Spacing to other contacts (shorted)           |

|                                           |                                                  |           | 6.3                                             | Spacing in array                              |

| 2. Active (Diffusion)                     |                                                  |           | 6.4                                             | Active overlap two opposite sides/other sides |

| 2.1                                       | Width                                            | 0.08      | 6.5                                             | Metal1 overlap, all sides                     |

| 2.2                                       | Space                                            | 0.11      | 6.6                                             | or Metal1 overlap, two sides/other sides      |

| 2.3                                       | Source/drain spacing to well                     | 0.16      | 6.7                                             | Spacing to gate                               |

| 2.4                                       | Source/drain margin to well                      | 0.16      | 6.8                                             | Spacing to select                             |

| 2.4                                       | p-active spacing to well                         | 0.16      | 6.9                                             | Margin to select                              |

| 2.4                                       | n-active margin to well                          | 0.16      |                                                 |                                               |

| 3. Poly                                   |                                                  |           | 7. Metal1                                       |                                               |

| 3.1                                       | Width                                            | 0.06      | 7.1                                             | Width                                         |

| 3.2                                       | Space                                            | 0.13      | 7.2                                             | Space short run (< 0.38) and narrow (<0.2)    |

| 3.3                                       | Gate overlap of active                           | 0.14      | 7.3                                             | Space longer run (<0.42) and wider (<0.42)    |

| 3.4                                       | Active overlap of gate                           | 0.115     | 7.4                                             | or dense configuration                        |

| 3.5                                       | Field poly to active                             | 0.10      | 7.5                                             | Space longer run (<1.5) and wider (<1.5)      |

| 4. Select (pplus and nplus)               |                                                  |           | 8. Via1. Via2. Via3 and Via4: NO VIAS ON GATES! |                                               |

| 4.1                                       | Select space (overlap) to (of) channel           | 0.16      | 8.1                                             | Via size exactly                              |

| 4.2                                       | Select space (overlap) to (of) active            | 0.13      | 8.2                                             | Space to other vias in same layer             |

| 4.3                                       | Select space (overlap) to (of) substrate contact | 0.02      | 8.3                                             | Space in array                                |

| 4.4                                       | Min width and space                              | 0.18      | 8.4                                             | Overlap by bottom metal                       |

|                                           |                                                  |           | 8.5                                             | Overlap by top metal                          |

| 5. Contact to poly: NO CONTACTS ON GATES! |                                                  |           | 9. Metal 2 to Metal 5                           |                                               |

| 5.1                                       | Contact size exactly                             | 0.09x0.09 | 9.1                                             | Width                                         |

| 5.2                                       | Spacing to other contacts (shorted)              | 0.11      | 9.2                                             | Space                                         |

|                                           | Spacing in array                                 | 0.14      | 9.3                                             | Space to short metal                          |

| 5.3a                                      | Poly overlap, all sides                          | 0.03      |                                                 |                                               |

|                                           | or Poly overlap, two opposite sides/other sides  | 0.04/0.01 | 10. Metal 6 to Metal 7                          |                                               |

| 5.4                                       | Metal1 overlap all sides                         | 0.025     | 9.1                                             | Width                                         |

|                                           | or Metal 1 overlap to sides/other sides          | 0.04/0.0  | 9.2                                             | Space                                         |

| 5.5                                       | Spacing to active                                | 0.14      |                                                 |                                               |

## 65 nm CMOS Design Rules

---

## **65 nm CMOS Design Rules**