# Power and performance limits

DAT116, Dec 6 2018

[larssv@chalmers.se](mailto:larssv@chalmers.se)

# ADC power limit

- ADC frequently critical component for mixed-signal system

- Fundamental limits on power dissipation

- Some system architectures are not buildable!

- Investigate limit, illustrate with recent data (Murmann; uploaded)

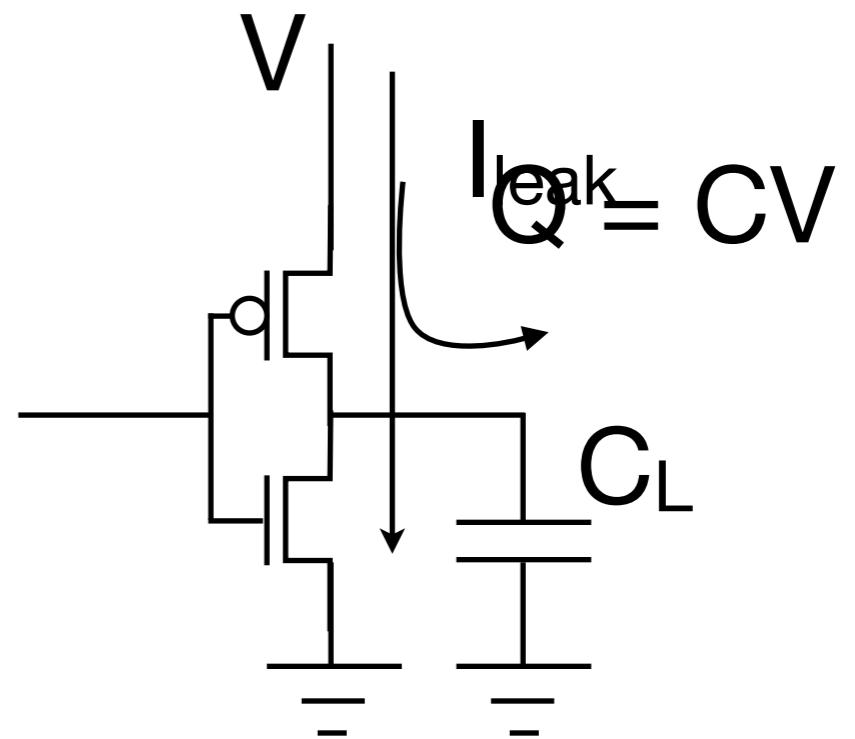

# Digital circuit power

- Simple case: inverter + C

- $P_{\text{total}} = P_{\text{active}} + P_{\text{leakage}}$

- $P_{\text{active}} \approx \beta_1 \cdot f_{\text{ck}} \cdot C_L \cdot V^2$

- $P_{\text{leakage}} = I_{\text{leak}} \cdot V$

$\approx \mu \cdot I_{\text{sat}} \cdot V$

$\approx \mu \cdot (C_L V / (t_{\text{ck}} / \beta_2)) \cdot V$

$\approx \mu \cdot \beta_2 \cdot f_{\text{ck}} \cdot C_L \cdot V^2$

Reduction: keep  $C_L$ ,  $V$ ,  $f_{\text{ck}}$  small

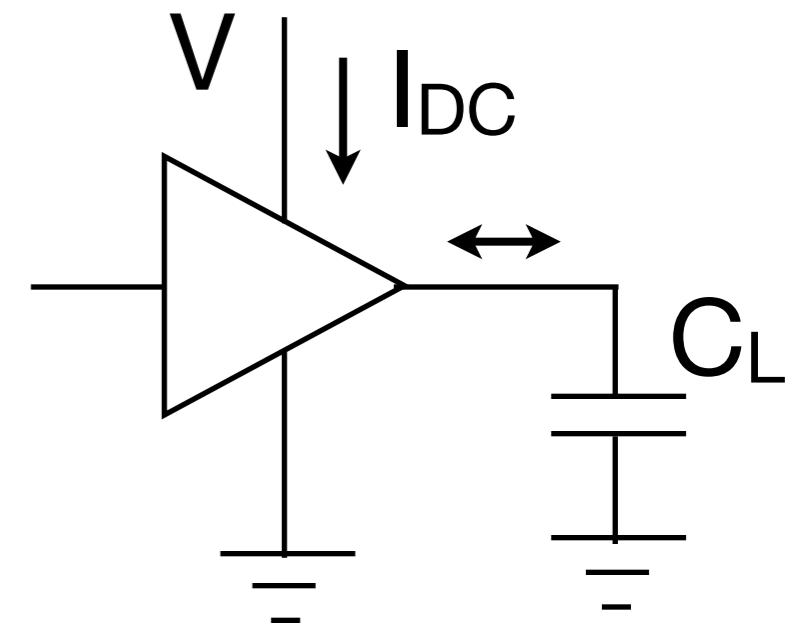

# Analog circuit power

- Simple case: “class-A” driver circuit

- Constant current draw

- Then,  $P_{\text{analog}} = I_{\text{DC}} \cdot V$

- $I_{\text{DC}}$  chosen according to load

- If capacitive load  $C_L$ , must be able to cover swing in one cycle (slew rate)

- So,  $P_{\text{analog}} = I_{\text{DC}} \cdot V \approx (C_L V / \beta_3 t_{\text{ck}}) \cdot V$

$= f_{\text{ck}} \cdot C_L \cdot V^2 / \beta_3$

Reduction: keep  $C_L, V, f_{\text{ck}}$  small

[Assuming rail-to-rail swing]

# Limits?

- Minimum  $f_{ck}$  set by signal bandwidth (Nyquist etc.)

- Minimum  $V$  set by performance requirements

- Switching speed, analog bandwidth

- .... so ultimately by signal bandwidth...

- $C$  remains!

- How small can it be?

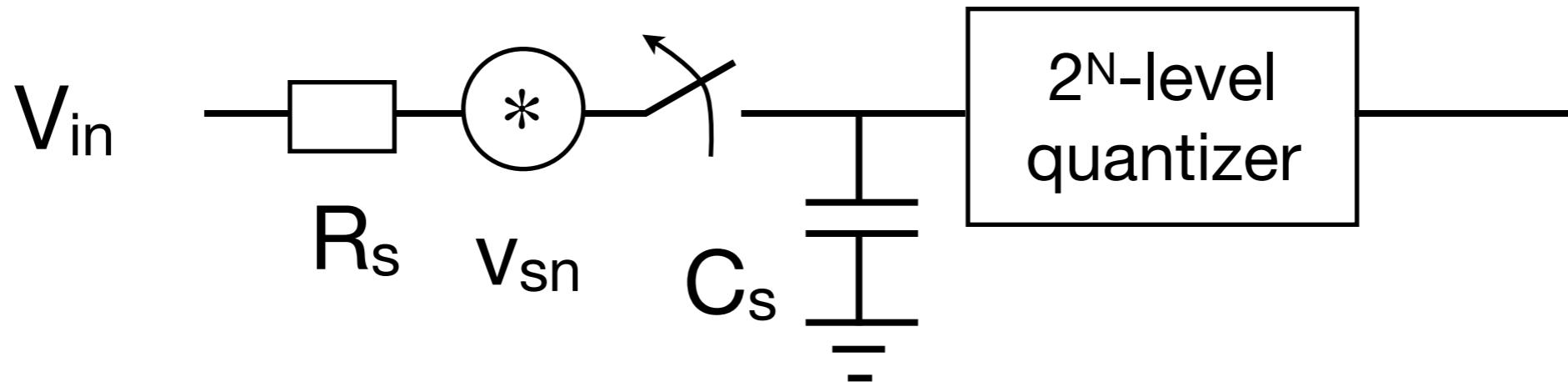

# Recall sampler kT/C noise

- $v_{sn}$  in series with  $V_{in}$

- $V_{in} + v_{sn}$  sampled on capacitance

$$\overline{v_{sn}^2} = kT/C_s$$

- Need large  $C_s$  for low  $\overline{v_{sn}^2}$

- Cost: area, power

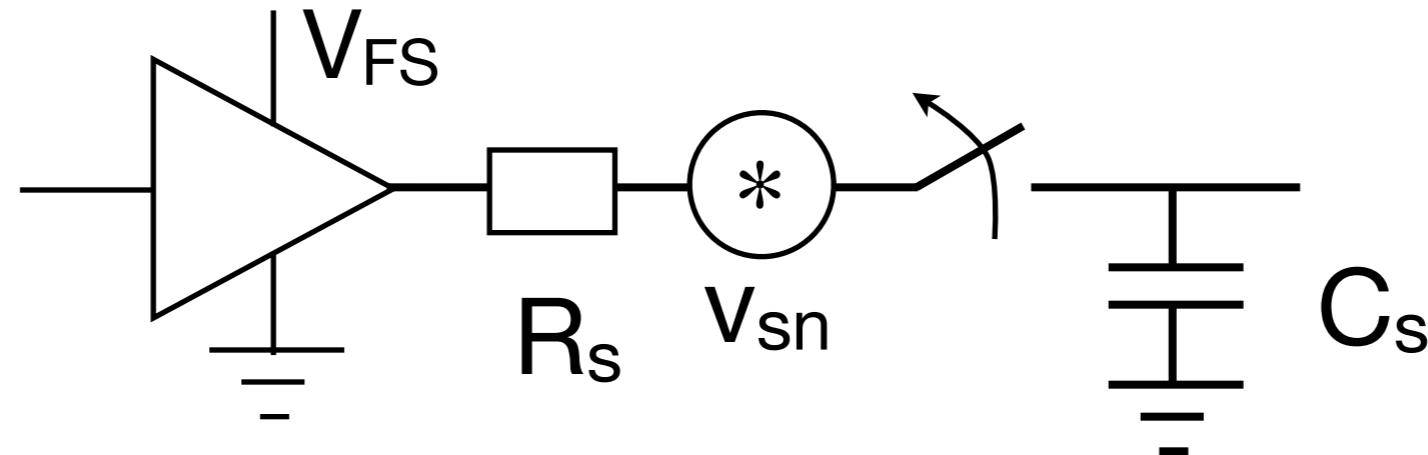

# Recall quantization noise

- Quantization noise depends on resolution

$$\overline{v_{qn}^2} = \Delta^2 / 12 = (V_{FS} / 2^N)^2 / 12$$

- Need high resolution for low quantization noise

- Cost: Component count, area, and/or clock rate

# Noise addition

- Uncorrelated noise powers may be added

- Adding sample noise and quantization noise:

$$V_{ntot}^2 = V_{sn}^2 + V_{qn}^2$$

- No use overdesigning either term!

- Cost for diminishing benefit

- Yes, there are more noise sources...

- ...but let's keep it simple for now...

# A good choice for $C_s$

- Assumption: balanced design when  $v_{sn}^2 = v_{qn}^2$  ; then:

$$v_{sn}^2 = kT/C_s$$

$$v_{qn}^2 = (V_{FS} / 2^N)^2 / 12$$

$$kT/C_s = (V_{FS} / 2^N)^2 / 12$$

- $C_s$  expressed in  $V_{FS}$  and  $N$ :

$$C_s = (12 kT / V_{FS}^2) \cdot 2^{2N}$$

# C<sub>S</sub> values

$$C_S = (12 kT / V_{FS}^2) \cdot 2^{2N}$$

Factor 4 per bit (16 per 2 bits)

| N  | C <sub>S</sub> |

|----|----------------|

| 4  | 13 aF          |

| 6  | 0.2 fF         |

| 8  | 3 fF           |

| 10 | 52 fF          |

| 12 | 0.8 pF         |

| 14 | 13 pF          |

| 16 | 214 pF         |

On-chip example:

- 0.18  $\mu$ m process

- $V_{FS} = 1.0$  V

- Gate cap of smallest transistor:  $\sim 0.9$  fF

- $C_S$  will not limit performance below 8 bits

- $13 \text{ pF} \sim 6000 \mu\text{m}^2$

- SRAM:  $\sim 100 \mu\text{m}^2 / \text{bit}$

High sample cap cost at high end!

# What drives the sampler?

- Sample capacitance is load of some analog circuit!

- Simple assumption: class-A driver, best efficiency

- $P_s = f_s \cdot C_s V_{FS}^2 = f_s \cdot ((12 kT / V_{FS}^2) \cdot 2^{2N}) V_{FS}^2$

$= 12 kT f_s 2^{2N}$

- Power needed to drive minimum  $C_s$  across full range from one sample to the next

- O/w full amplitude cannot be reached at Nyquist!

Independent of  $V_{FS}$ !

# Examples

$$P_S = 12 kT f_S 2^{2N}$$

$$[k = 1.38 \times 10^{-23}, T = 300]$$

- 10 bits, 10 MS/s:  $P_S = 0.5 \mu\text{W}$

- 14 bits, 100 MS/s:  $P_S = 1.3 \text{ mW}$

- 18 bits, 1 GS/s:  $P_S = 3.4 \text{ W}$

- 24 bits, 50 GS/s (from teaser video):  $P_S = 70 \text{ kW}$

# Absolute vs practical?

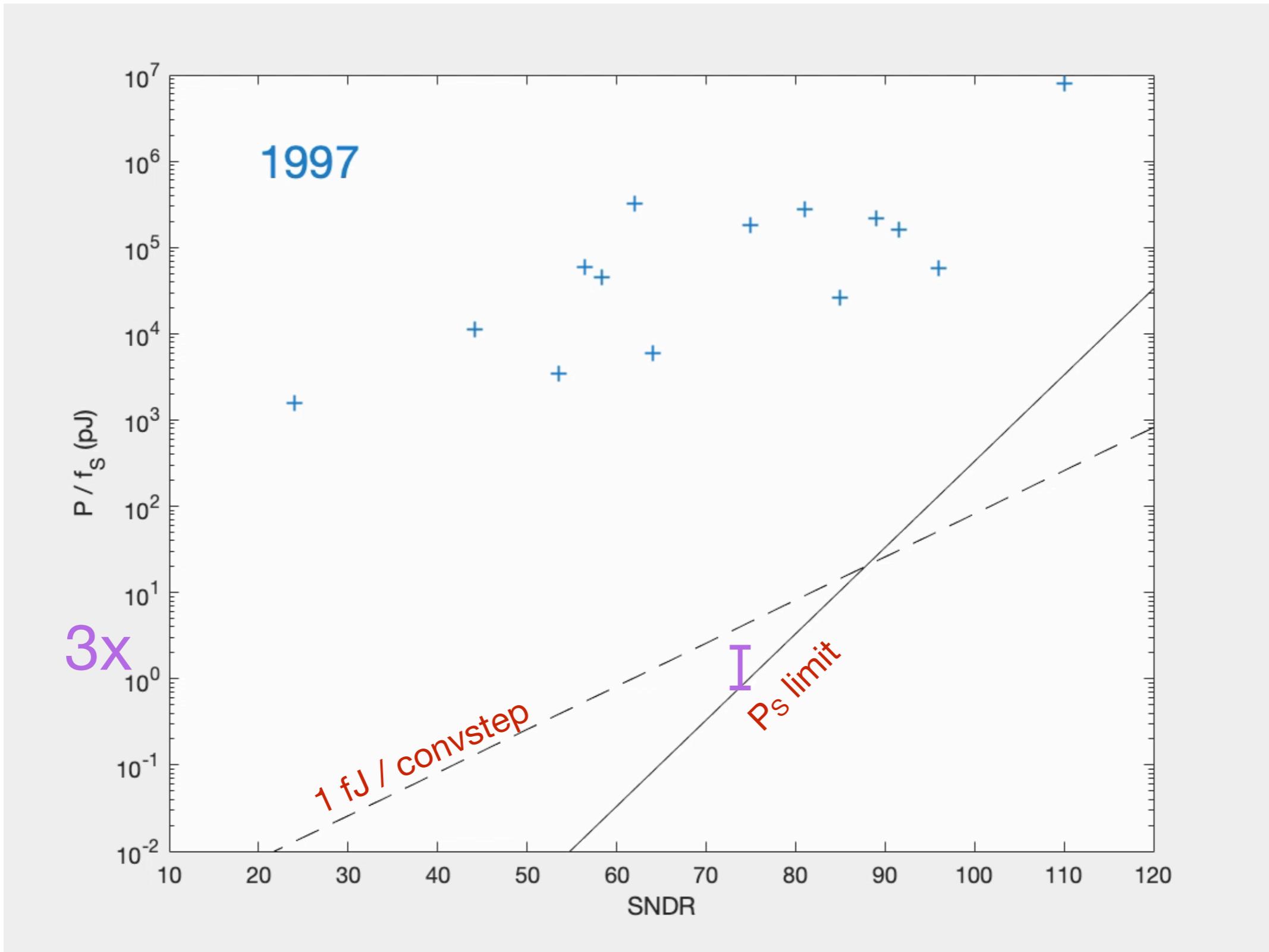

- $P_s = 12 kT f_s 2^{2N}$  is “limit” for power!

- ...under certain assumptions...

- Note: limit of “sample power” only!

- Rest of ADC needs power too

- Total power necessarily larger than  $P_s$

- Practical state of the art?

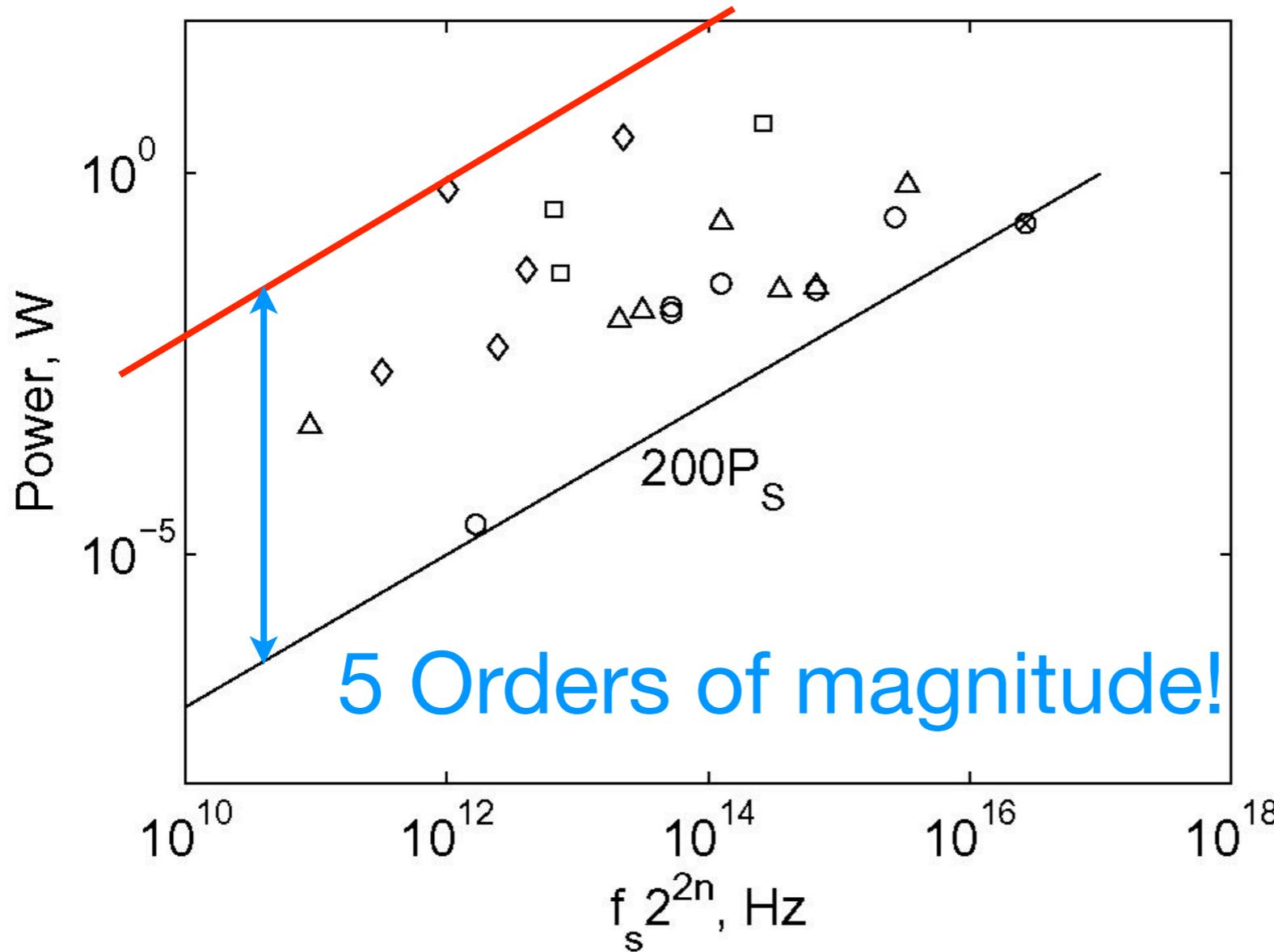

# Reality check

$\triangle, \circ$ : Pipelined

$\square, \diamond$ : Flash

High-speed converters

ISSCC 2002,

2006

# Performance points

- $P / P_s = 200 \dots 20000000$  for exceptional, high-speed converters (in 2006)... but:

- What about lower speeds?

- Does resolution matter?

- What happens with technology progression?

- Can we find some common Figures of Merit (FoMs) to compare different ADC designs?

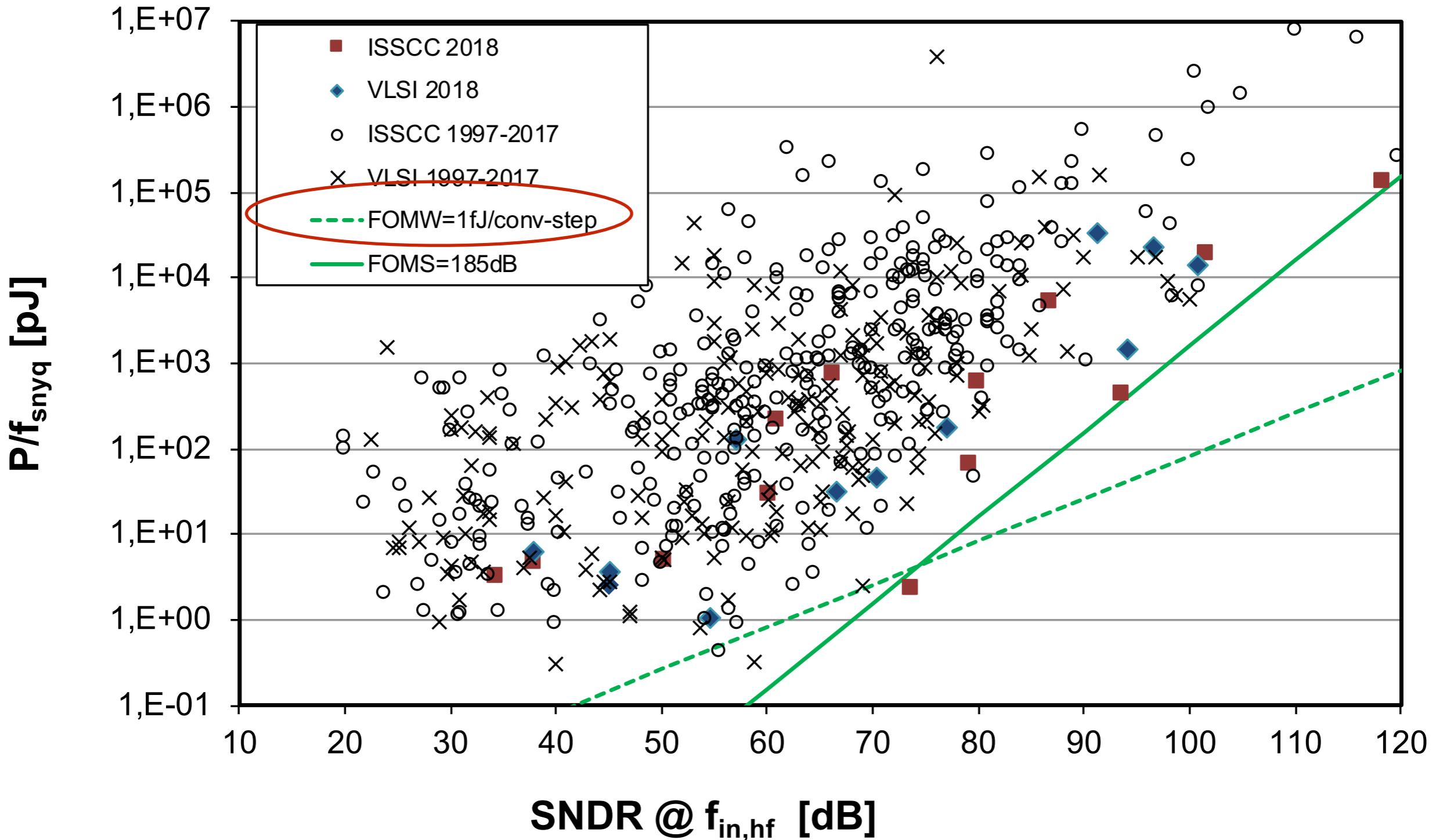

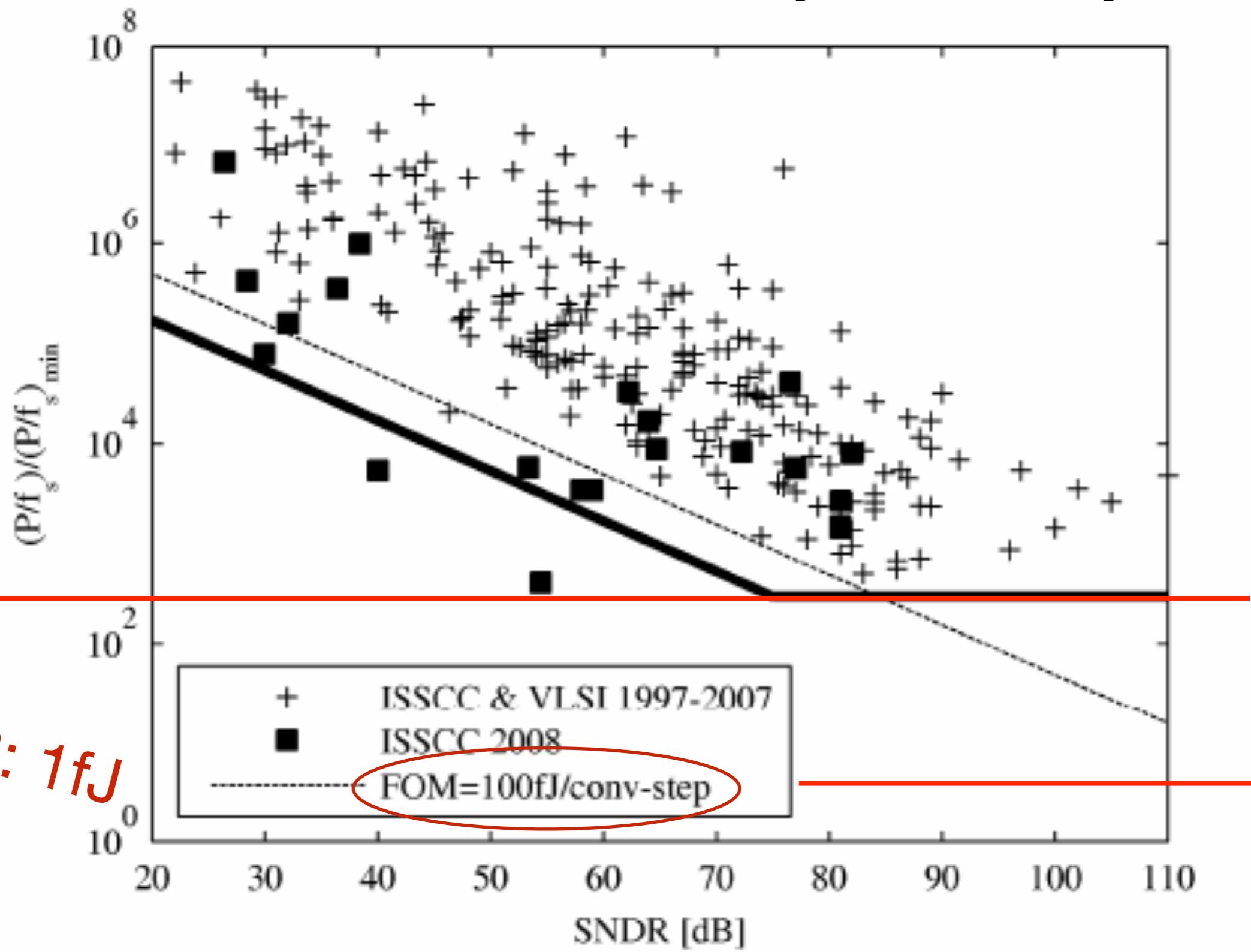

# Example FoM

- Compare converter designs wrt power

- Compensate for  $f_s$ , SNDR

- Low  $f_s$ : should be cheap

- Low SNDR: should be cheap

- $FoM = P / (f_s \cdot 2^{ENOB})$  [or similar expression; see Maloberti chap. 2]

- Loosely, energy per “conversion step”

- Low FoM values are better!

- Applied to 537 excellent designs (ISSCC, VLSI Symposium, 1997 – 2018)

$$ENOB = (SNDR - 1.76) / 6.02$$

# ISSCC+VLSIS FoMs

# ISSCC+VLSIS FoMs

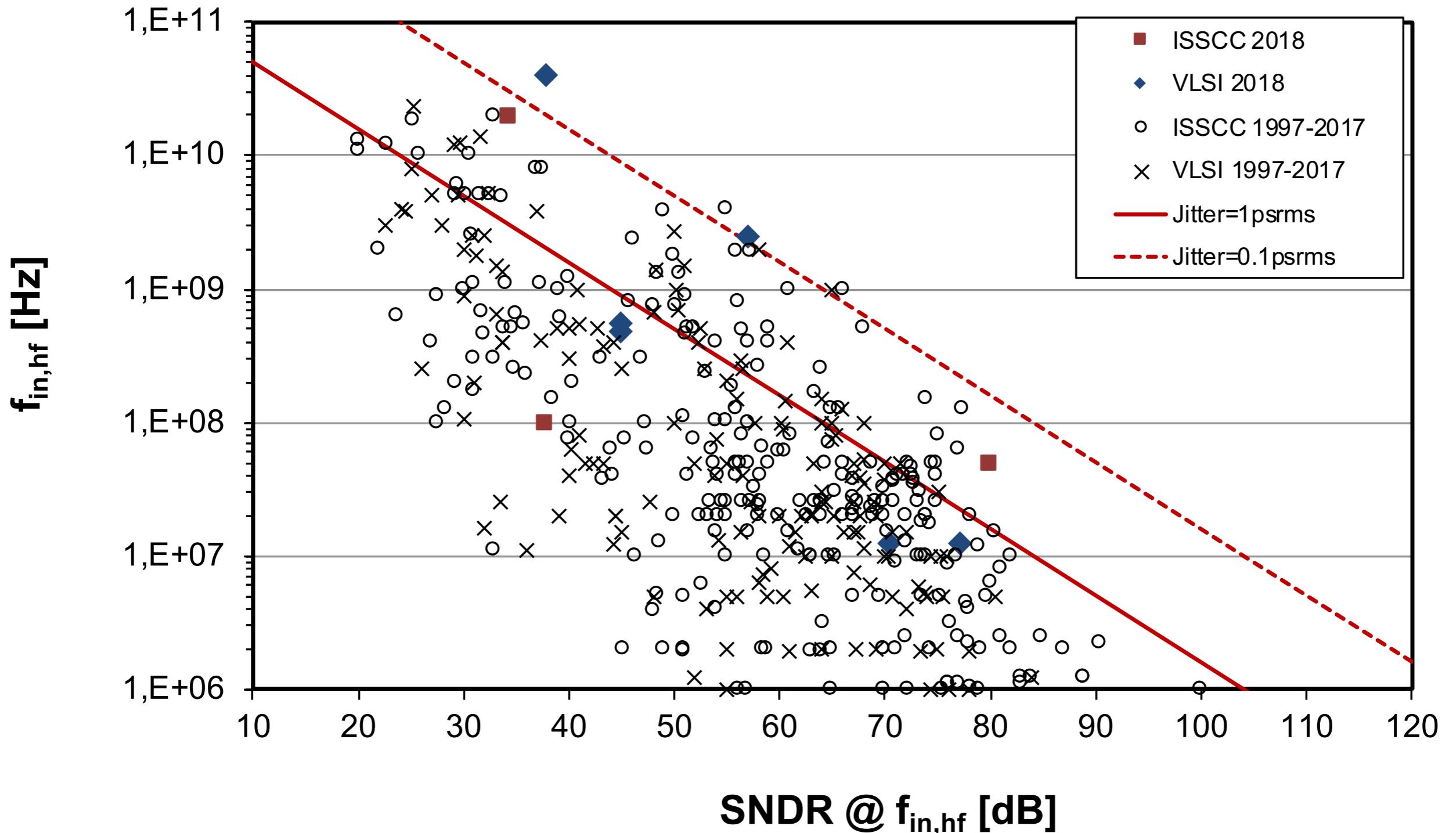

# Jitter limit

# Noise limit (2008)

# EADC VS ENAND

| SNDR (dB) | $E_{ADC}$    | $E_{ADC} / E_{NAND}$ |

|-----------|--------------|----------------------|

| 30        | 21 nJ        | 4700                 |

| 50        | 168 nJ       | 38000                |

| 70        | 1.35 $\mu$ J | 300000               |

| 90        | 10.8 $\mu$ J | 2400000              |

- Complete ADC energy per conversion (in 2008) vs energy of one NAND-gate logic transition in 90-nm CMOS

- Digital logic more “affordable” for higher resolutions!

- Even more in newer technologies

- Increasingly attractive to use digital methods to improve performance!

Later: Digital assist

# Analog? D/A?

- ADCs show fundamental limits clearly!

- Other limits (hard/soft) apply elsewhere

- All capacitances show  $kT/C$  noise!

- Filters, oscillators, etc

- For D/As, main problem often matching

- Addressed by digital means

# Summary

- Sample noise sets energy limit on ADCs as we know them

- Present ADCs close in on these limits!

- Future progress likely mostly at lower resolutions

- Shrinking voltage swing