# **DAT110**

# **METHODS FOR ELECTRONIC SYSTEM**

# **DESIGN AND VERIFICATION**

Per Larsson-Edefors

VLSI Research Group

# **LECTURE 8:**

# **RELIABILITY AND TEST.**

# **Device scaling and reliability**

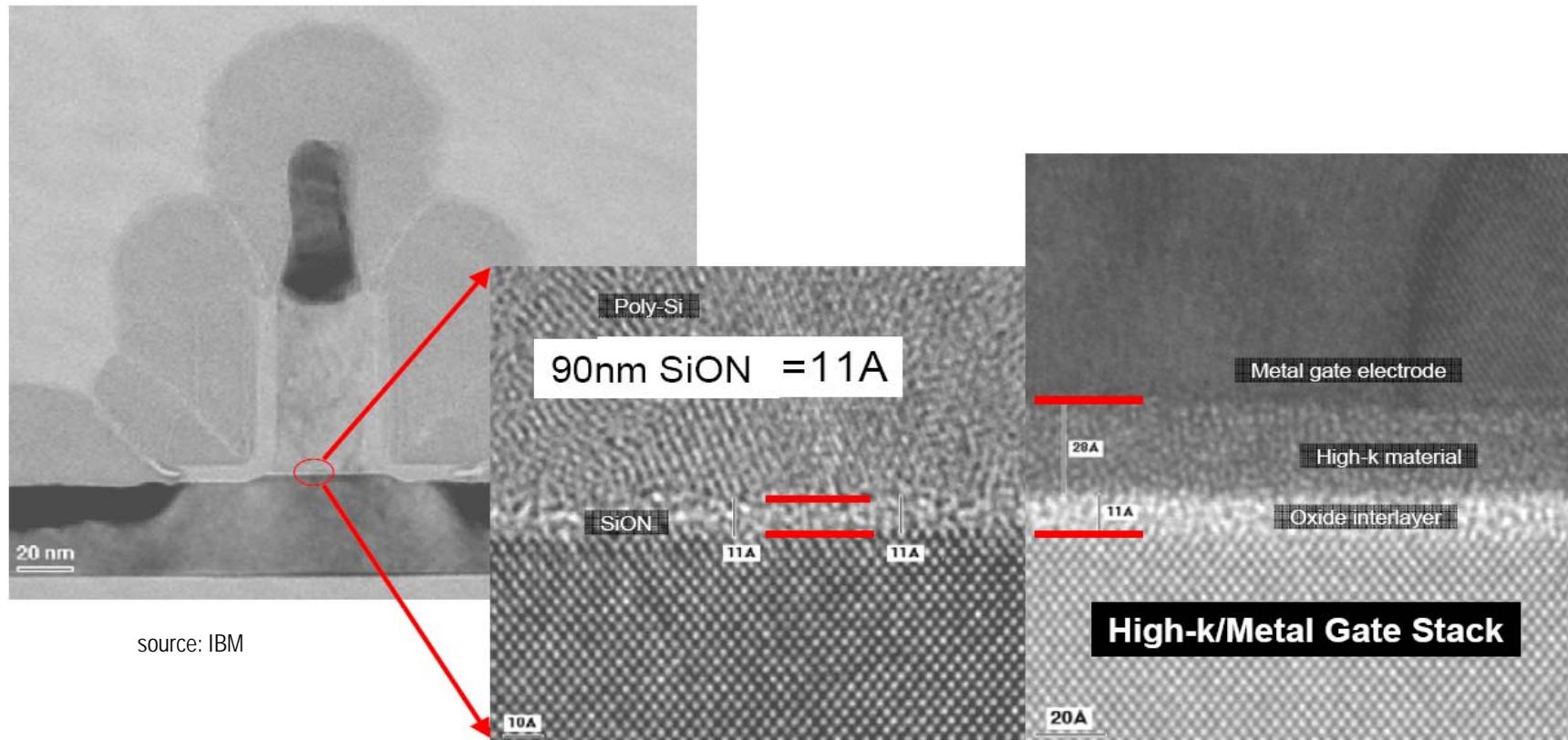

# SCALED TRANSISTORS: THIN OXIDES

- ◆ Consider insulator thickness: Silicon atom diameter is 0.26 nm.

**90nm Gate Dielectric:**

$T_{inv} = 19\text{A}$

$ToxGL = 11\text{A}$

**High-k/Metal Gate Stack:**

$T_{inv} = 15.5\text{A}$

$ToxGL = 20\text{A}$

## **THE OXIDE TUNNELING PROBLEM**

- ◆ High- $k$  dielectric insulators enable a larger physical insulator thickness, without losing the gate's control of channel properties.

- ◆ A larger physical thickness reduces tunneling.

- ◆ Many high- $k$  materials have been studied:

- Aluminum oxide ( $\text{Al}_2\text{O}_3$ ), titanium dioxide ( $\text{TiO}_2$ ), tantalum pentoxide ( $\text{Ta}_2\text{O}_5$ ), hafnium dioxide ( $\text{HfO}_2$ ), hafnium silicate ( $\text{HfSiO}_4$ ), zirconium oxide ( $\text{ZrO}_2$ ), zirconium silicate ( $\text{ZrSiO}_4$ ), lanthanum oxide ( $\text{La}_2\text{O}_3$ ) ...

- ◆ Intel's 45-nm process: Hafnium-based insulator ( $k \approx 25$ ).

# **SCALING DEVICES MAKES THEM SENSITIVE**

## ◆ Thin oxides.

- High electric fields across oxide  $\Rightarrow$  the current punches through  $\Rightarrow$  the insulating property is destroyed.

- I/O transistors employ thick oxide.

## ◆ Thin and narrow wires.

- Cannot carry large currents.

- High resistance.

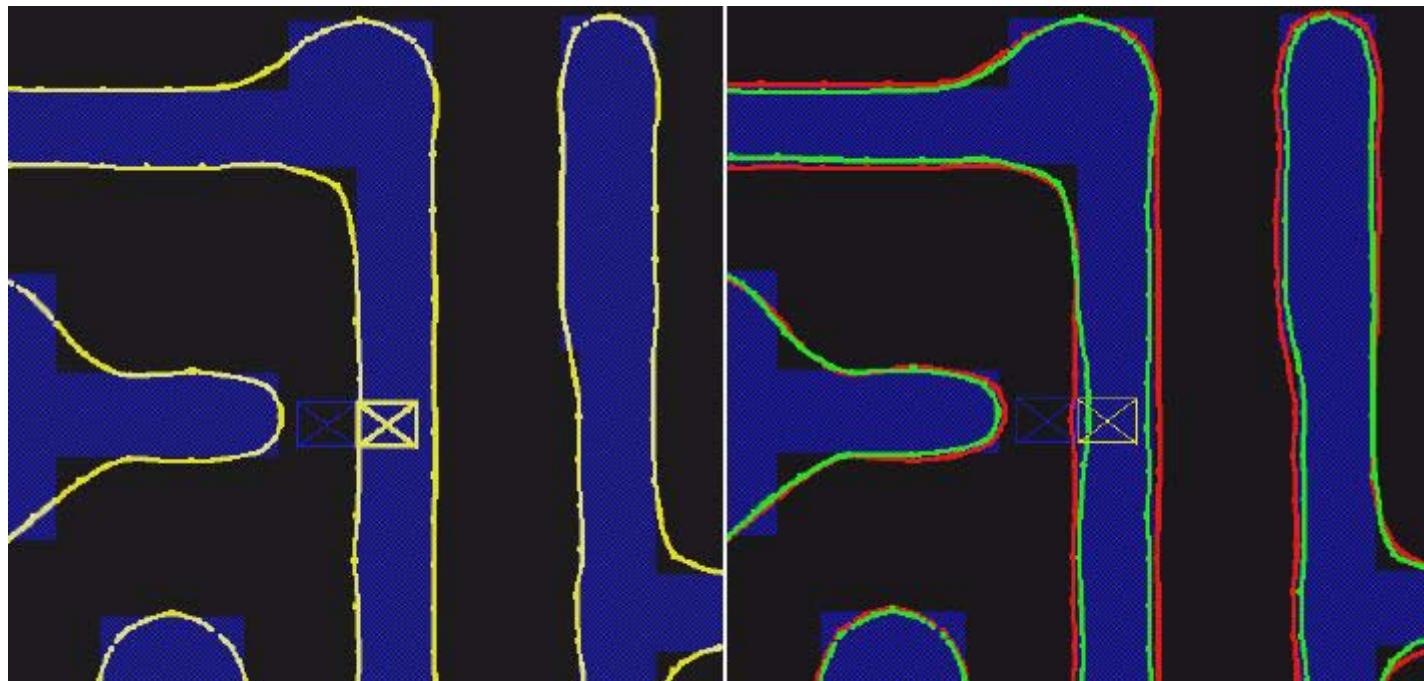

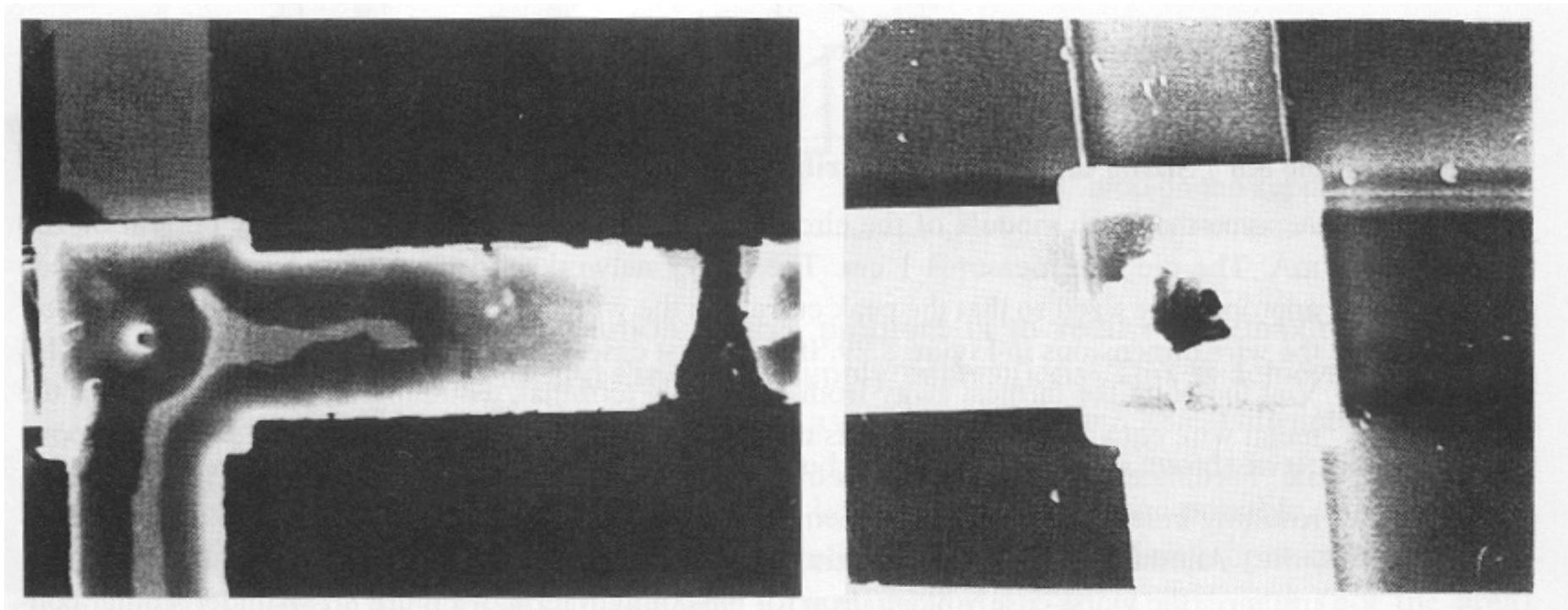

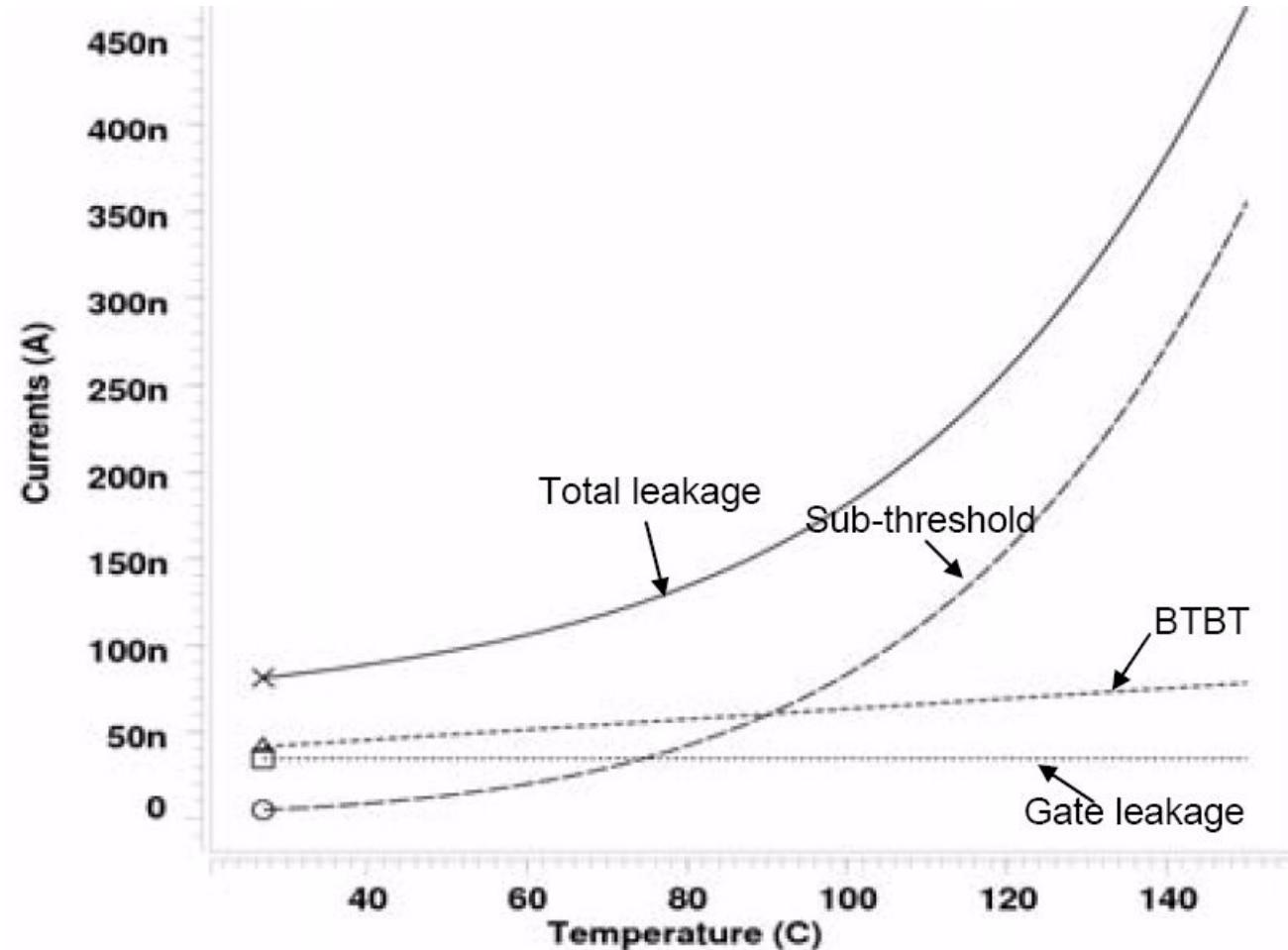

## AYOUT HOTSPOTS

- ◆ Hotspots: Specific patterns prone to bridging (shorts) or pinching (opens), as fabrication process drifts away from optimum condition.

Source: Roseboom

## **TRENDS**

- ◆ Because of shrinking geometries, need for new terms:

- Design For Manufacturing (DFM)

- Design For Yield (DFY)

- ◆ Lithography using 193 nm light sources still common.

- ◆ TSMC intends to use extreme ultraviolet (EUV) for their 7-nm technology.

- ◆ Similar message from Samsung that intends to develop EUV-based 7-nm technology (EUV from ASML).

# **Failure mechanisms**

## **WHAT CAN GO (SERIOUSLY) WRONG?**

Apart from our own design mistakes, there are a number of catastrophic failures we may encounter:

- ◆ Catastrophic timing problems (hold violations).

- ◆ Power distribution problems (electromigration).

- ◆ Ageing problems (NBTI, HCI, TDDB).

- ◆ Thermal runaway problems (burn-in).

- ◆ Manufacturing problems in foundry/fab.

- ◆ *Single-event upsets could be considered for this list, but they are usually not catastrophic.*

## **WHAT CAN GO (SERIOUSLY) WRONG?**

- ◆ Catastrophic timing problems (hold violations).

- ◆ Power distribution problems (electromigration).

- ◆ Ageing problems (NBTI, HCI, TDDB).

- ◆ Thermal runaway problems (burn-in).

- ◆ Manufacturing problems in foundry/fab.

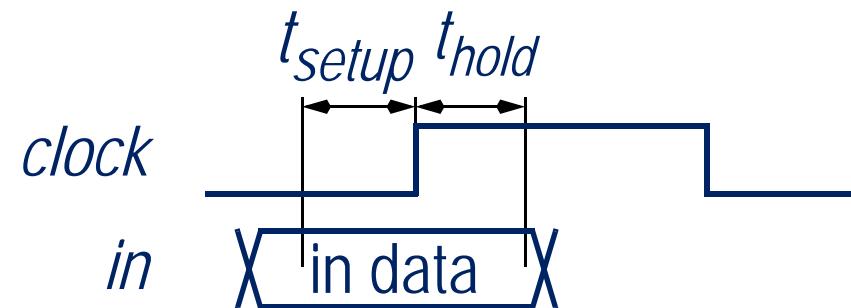

## **REPETITION: TIMING PROPERTIES OF A FLIP-FLOP**

- ◆ Setup time/hold time is the minimal time before/after the clock edge that stable data needs to be available at the flip-flop input for functionality to be ensured.

- ◆ Recovery time/removal time is used for set and reset signals.

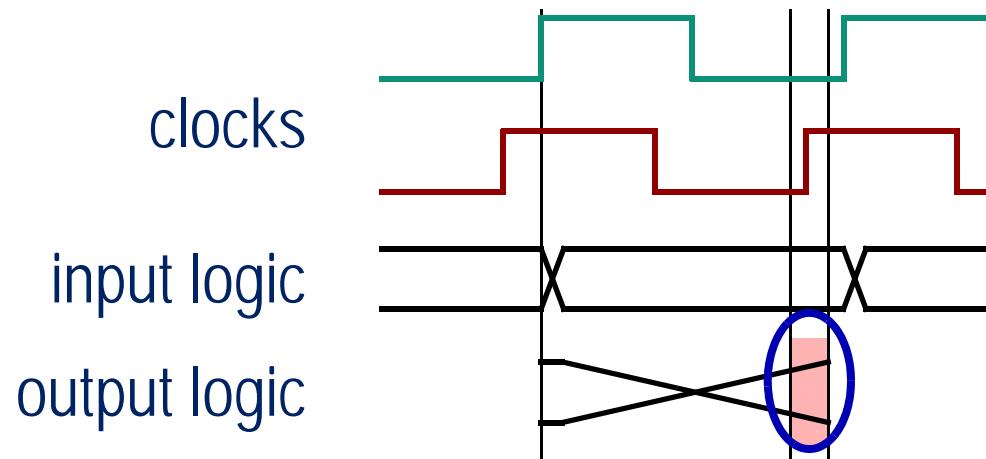

# NEGATIVE SKEW - CLOCK FLOWS AGAINST DATA

- ◆ Clock reaches **capture FF** before **launch FF**: Negative skew.

- ◆ Race cannot happen.

- ◆ Negative skew reduces the available evaluation time:

We need to insert an extra design margin on the delay.

- ◆ If **capture FF** samples the wrong data, we have a setup violation.

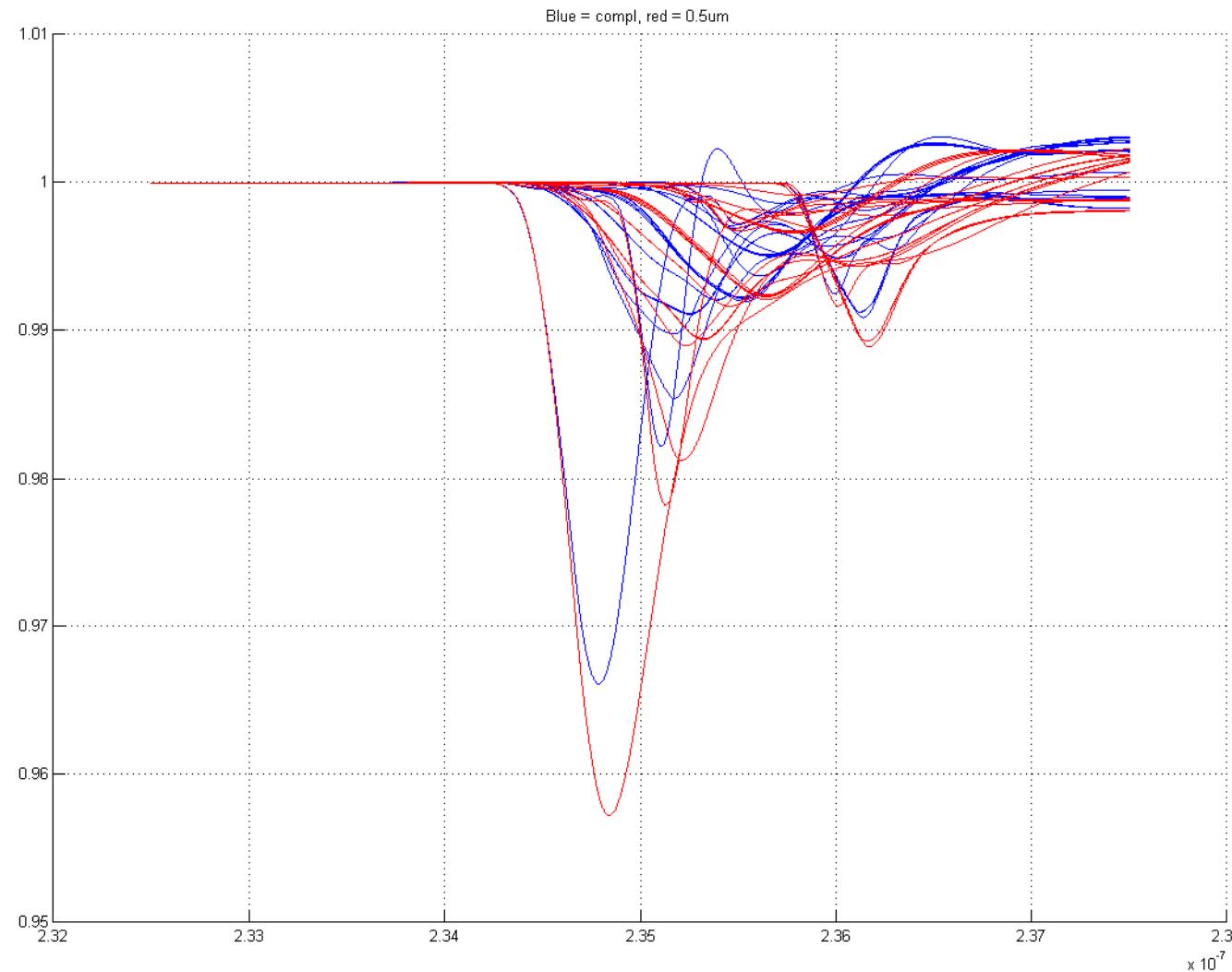

# POSITIVE SKEW - CLOCK FLOWS WITH DATA

- ◆ Clock reaches **capture FF after launch FF**: Positive skew.

- ◆ If logic has very short delay, we may suffer from a hold violation (race).

- ◆ Hold violations could manifest inside shift registers or between FFs responsible for inter-block communication:

- Cause of the latter: The respective clocks of the two blocks are produced in different clock trees and the relative skew is hard to control.

## **UNINTENTIONAL CLOCK SKEW IS CAUSED BY ...**

- ◆ Variation in effective channel length.

- ◆ Variation in threshold voltage  $V_T$ .

- ◆ Variation in ILD (inter-layer dielectric) thickness  $\Rightarrow$  variation in  $C$ .

- ◆ Variation in supply voltage  $V_{DD}$ .

- ◆ Variation in temperature  $T$ .

- ◆ Signal coupling - crosstalk.

- ◆ Design choices, such as clock gating.

## **COMMENTS ON POSITIVE AND NEGATIVE SKEW**

### ◆ Negative clock skew.

- Race can never happen.

- Performance goes down. If you experience setup violations, reduce clock frequency to make the design work.

### ◆ Positive clock skew.

- Race can happen.

- If you experience hold violations

**your design is beyond recovery:**

Changing clock frequency does not help.

# **TIMING CLOSURE => CONTROLLING CLOCK!**

Source: AMD

- ◆ Controlling the clock arrival at flip-flops is essential to synchronous behavior: Clock skew needs to be controlled.

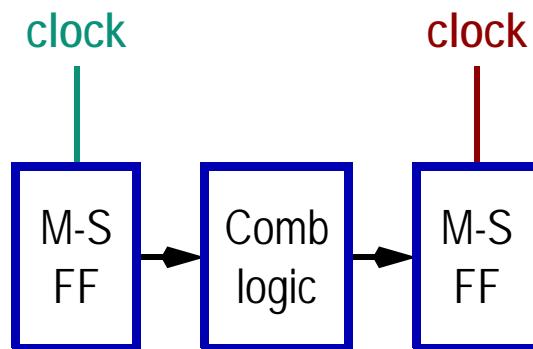

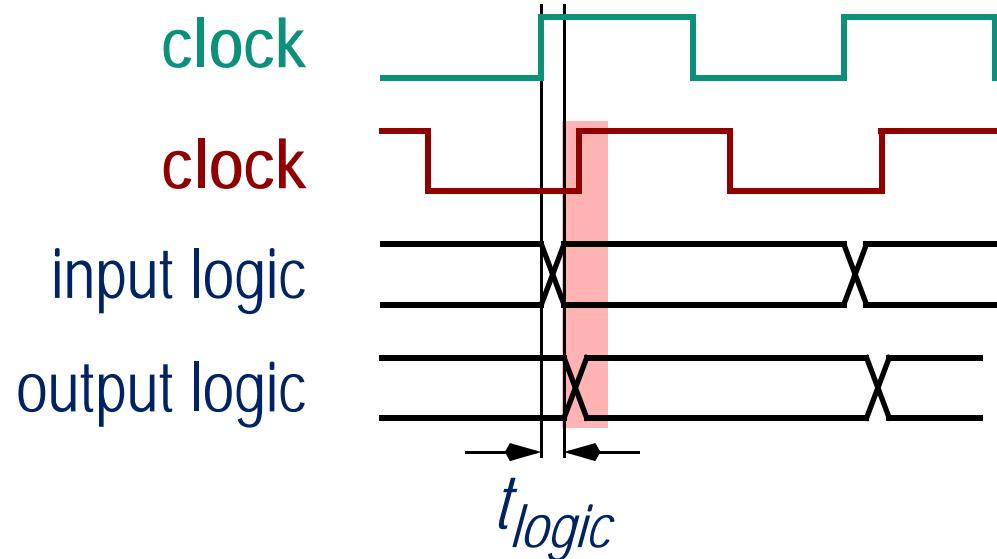

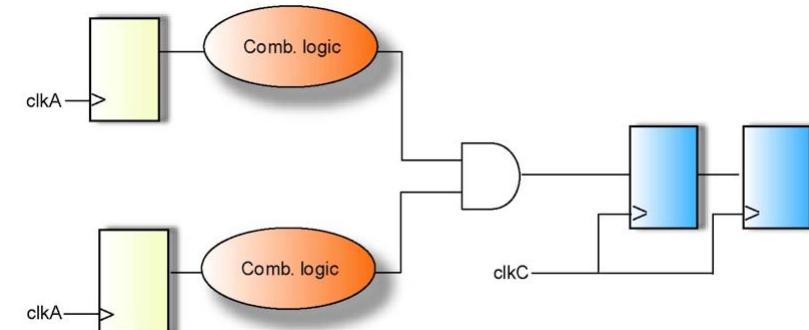

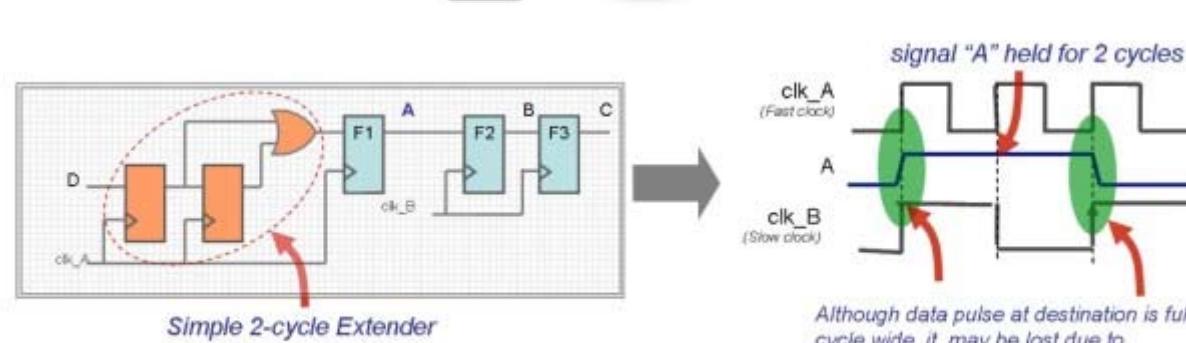

# CLOCK DOMAIN CROSSING (CDC) ISSUES

- ◆ Issues with e.g. cross-domain fan-ins: Rather synchronize first, then perform logic op:

- ◆ Issues with hold time violations on fast-to-slow clock crossings:

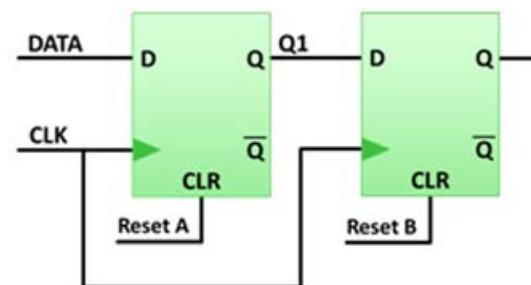

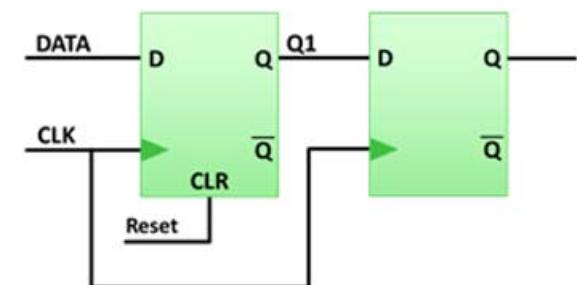

- ◆ Issues with Reset Domain Crossings (RDCs).

Figure 2a: Asynchronous Resets on Source and Destination Flop

Figure 2b: Asynchronous Reset on Source Flop Only

Source: Synopsys/Atrenta (Spyglass).

## **WHAT CAN GO (SERIOUSLY) WRONG?**

- ◆ Catastrophic timing problems (hold violations).

- ◆ Power distribution problems (electromigration).

- ◆ Ageing problems (NBTI, HCI, TDDB).

- ◆ Thermal runaway problems (burn-in).

- ◆ Manufacturing problems in foundry/fab.

## **POWER RAILS AND ELECTROMIGRATION**

- ◆ When designing power rails for large circuits we must pay attention to the width of the wires [Lab exercise 4].

- ◆ Electromigration is the process of electric current moving metal atoms (ions) in the wires, making them break after some (quite long) time.

- Especially 90° wire layout corners are sensitive.

- ◆ For AC rails (clock + signals) the effect of electromigration is an order of magnitude lower than for DC rails.

- In scaled techs, signal wires can suffer from electromigration.

- ◆ Typical limiting DC value:  $1.0 \text{ mA} / \mu\text{m width}$ .

# ELECTROMIGRATION

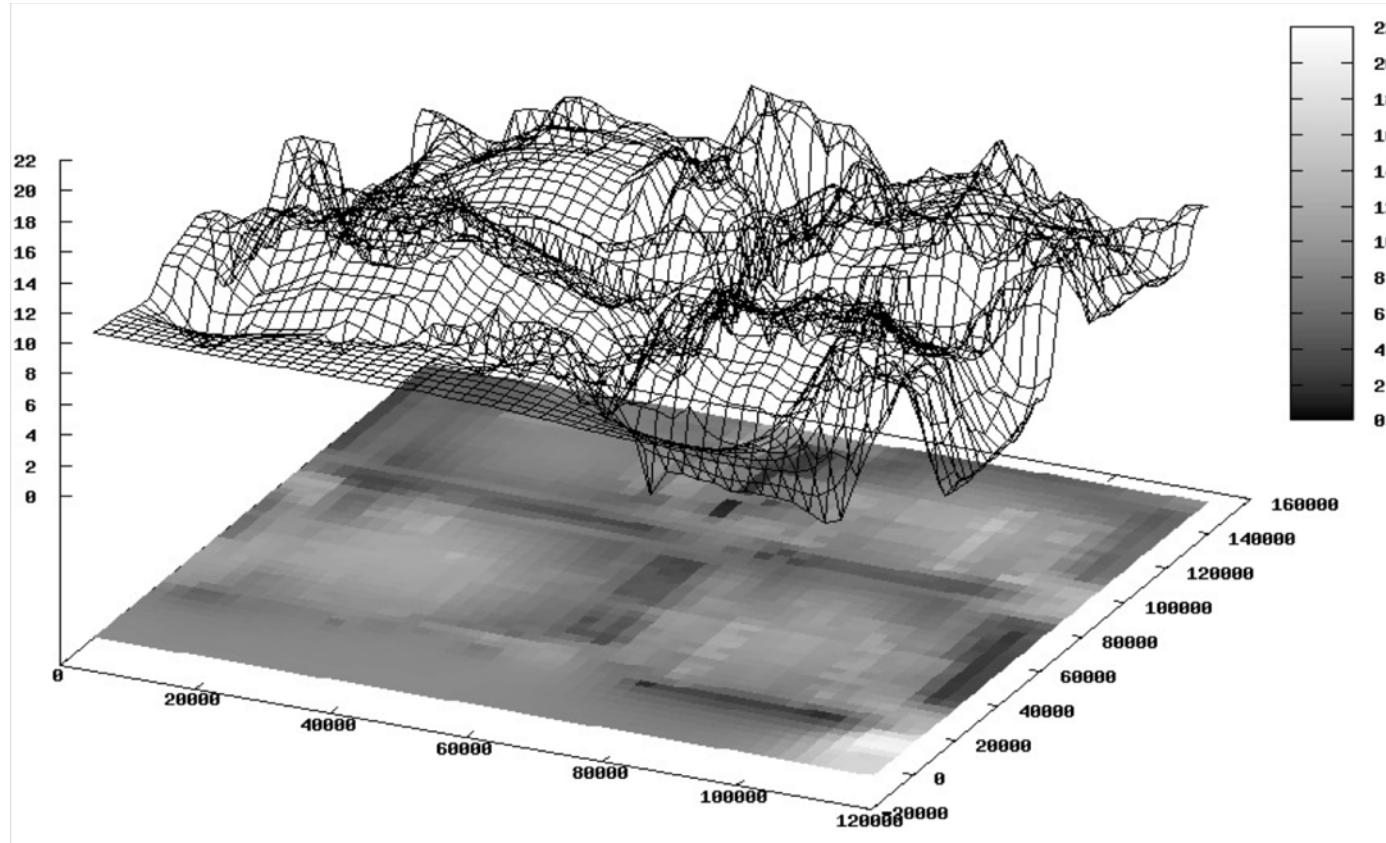

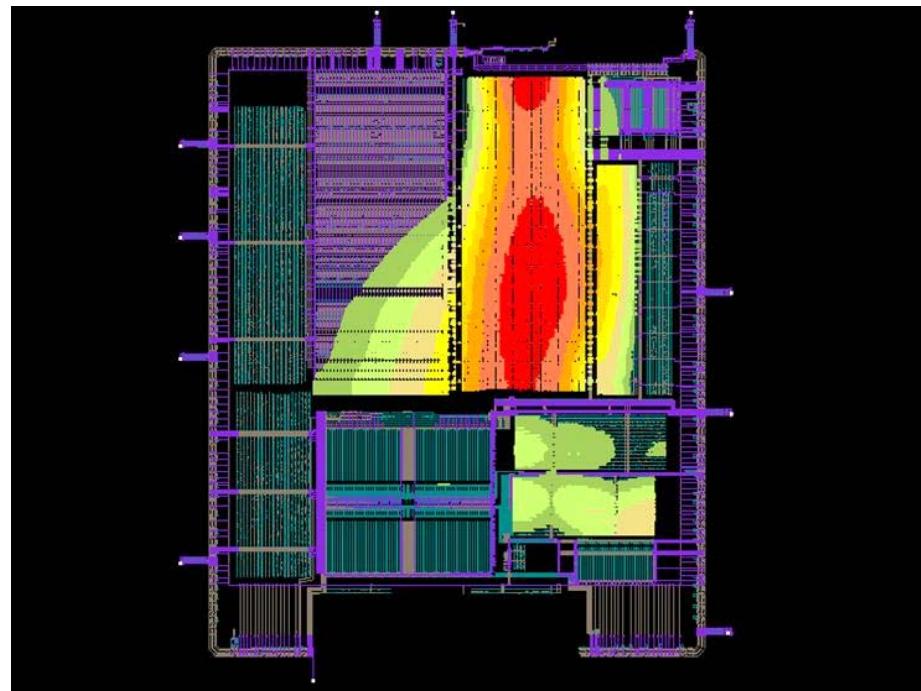

## **IR DROPS**

- ◆ As supply voltage wires get thinner and narrower, an increasing resistance gives rise to increasing voltage drops  $\Rightarrow$  gate delay increases.

Source: Cadence.

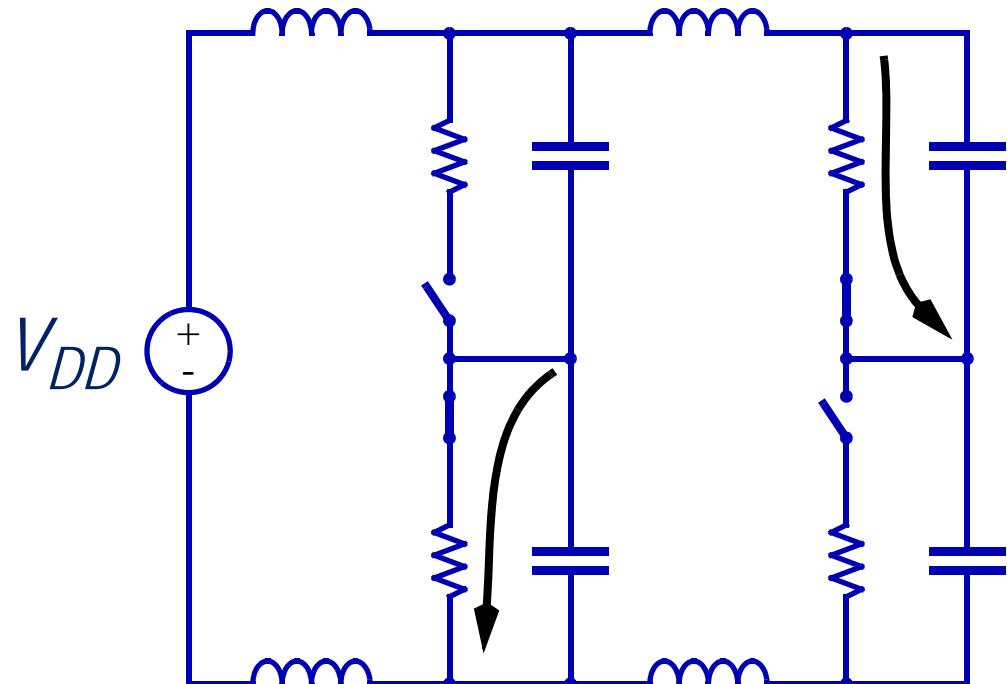

## dI/dt NOISE

- ◆ Synchronous systems have high peak currents.

- ◆ The power rail network acts as inductance = low-pass filter.

- ◆ Power rail voltage will vary:

$$\Delta V = -L \frac{dI}{dt}$$

. This is known as switching ( $dI/dt$ ) noise.

- ◆ Decoupling capacitances can somewhat mitigate the problem of switching noise.

## **COMMENTS ON POWER DISTRIBUTION**

- ◆ Electromigration can lead to catastrophic failures, from which the chip cannot recover.

- ◆ IR drops and switching noise dynamically affect performance during the operation of a chip.

# SIMULATION OF POWER GRID / ANIMATION

## **WHAT CAN GO (SERIOUSLY) WRONG?**

- ◆ Catastrophic timing problems (hold violations).

- ◆ Power distribution problems (electromigration).

- ◆ Ageing problems (NBTI, HCI, TDDB).

- ◆ Thermal runaway problems (burn-in).

- ◆ Manufacturing problems in foundry/fab.

## **NEGATIVE BIAS TEMPERATURE INSTABILITY**

- ◆ NBTI = Negative Bias Temperature Instability makes a chip deteriorate over time.

- ◆ A gradual shift of threshold voltage over time in PMOSFET. NBTI gets worse ...

- with scaling of transistor geometry.

- as the electric field (V/m) across the insulator increases.

- as average device temperatures generally increase.

- ◆ As supply voltages have been dropping, the threshold shift has come to have a relatively large impact on performance.

## **MORE ON NBTI**

- ◆ Origin: Interface traps exist between insulator and channel.

Here holes can get stuck (when  $V_{GS} < 0$  for PMOSFET).

- ◆ Interface states + fixed charges are both positive for the PMOSFET and thus results in a negative shift of threshold voltage.

- In an NMOSFET, interface states and fixed charges are of different polarity. Therefore, they cancel each other.

- ◆ NBTI can cause immediate failures after burn-in.

- ◆ After burn-in the PMOSFETs may recover, but permanent damages that affect the ageing process are not uncommon.

## Hot-CARRIER EFFECT

- ◆ Also HCl = Hot Carrier Injection makes a chip deteriorate over time.

- ◆ "Hot" carriers have higher velocity than the thermal velocity,  $v_{th}$ :

- $$\frac{m \cdot v_{th}^2}{2} = \frac{kT}{2} \Rightarrow v_{th} = \sqrt{\frac{kT}{m}}$$

for electrons.

- ◆ Hot carriers are drifting in high electric fields, around the drain terminal, when  $|V_{DS}|$  is high.

Shorter gate length yields higher HCl.

- ◆ 1) Hot carriers collide with crystal atoms,

2) produce electron-hole pairs (impact ionization), after which

3) electrons and holes penetrate and destroy insulators.

## **TIME-DEPENDENT DIELECTRIC BREAKDOWN**

- ◆ TDDB = Time-Dependent Dielectric Breakdown

wears out the gate insulator over time,

leading to the formation of a conducting path to the substrate.

- ◆ High-quality insulators postpone the effect of TDDB.

- ◆ There is a trade off between

gate insulator thickness and operating voltage specifications

to achieve both speed and lifetime specifications.

## **WHAT CAN GO (SERIOUSLY) WRONG?**

- ◆ Catastrophic timing problems (hold violations).

- ◆ Power distribution problems (electromigration).

- ◆ Ageing problems (NBTI, HCI, TDDB).

- ◆ Thermal runaway problems (burn-in).

- ◆ Manufacturing problems in foundry/fab.

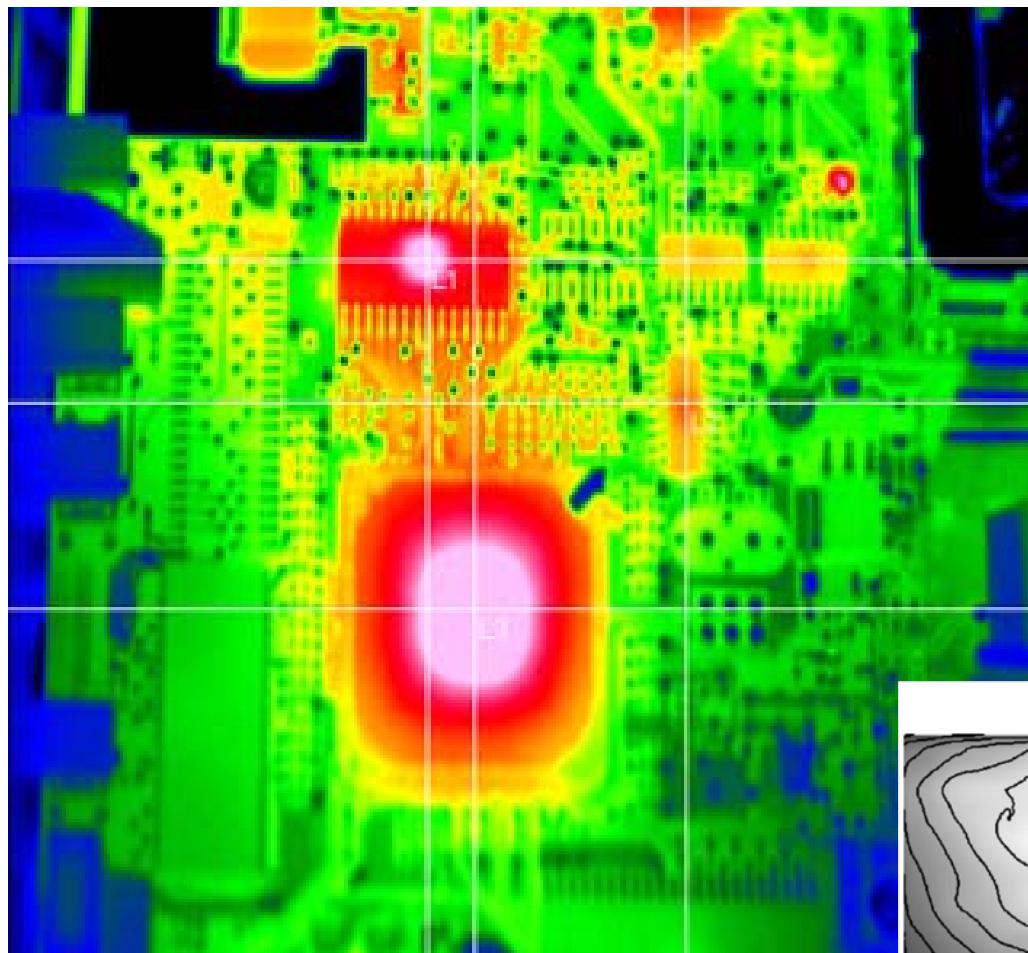

# HIGH TEMPERATURE IS HARMFUL

- ◆ Generally, high power dissipation leads to hot spots on boards and chips.

- ◆ Both absolute  $T$  and temperature gradients matter.

source: IBM

## **CHIP TEMPERATURE**

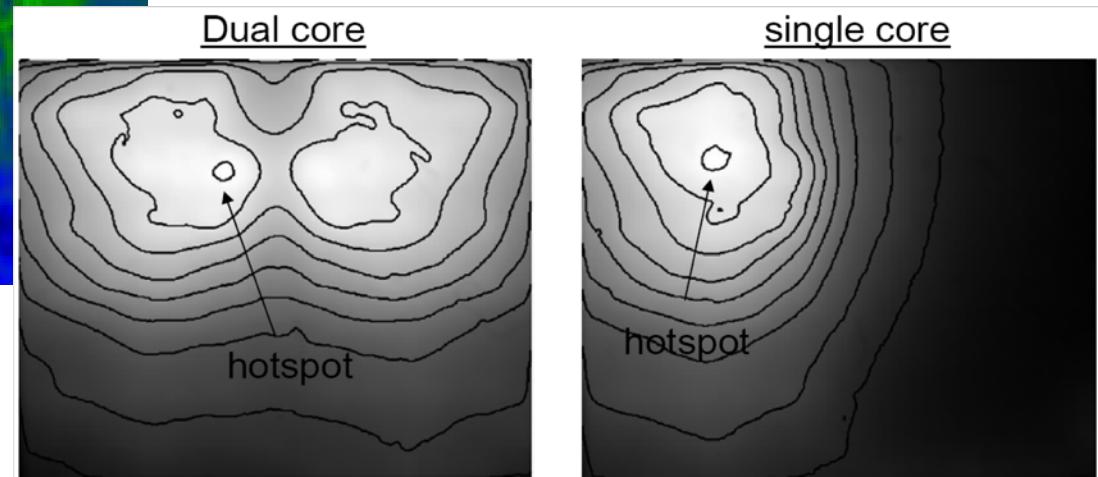

- ◆ Temperature is dependent on switching activity as well as leakage.

- ◆ Top temperatures can reach 110°C.

- ◆ Different areas of a chip may vary by ~40°C (memory is the coolest component).

- ◆ The die has a top passivation layer that acts as a “thermal blanket”; underneath there may be a thermal differential of as much as 45°C between the top metal layer and the silicon substrate.

- ◆ *More on burn-in later ...*

## **WHAT CAN GO (SERIOUSLY) WRONG?**

- ◆ Catastrophic timing problems (hold violations).

- ◆ Power distribution problems (electromigration).

- ◆ Ageing problems (NBTI, HCI, TDDB).

- ◆ Thermal runaway problems (burn-in).

- ◆ Manufacturing problems in foundry/fab.

## **MANUFACTURING DEFECTS 1(2)**

- ◆ Extra or missing materials.

- Dust particles on the mask, wafer surface or processing chemicals, e.g. photoresist  $\Rightarrow$  extra, unwanted material or unwanted etching of material.

- ◆ Gate Oxide Shorts (GOSs).

- Pinhole defects are common thin-ox defects: Chemical contamination, nitride cracking at oxidation, crystal defects ...

- *A GOS can be created in post-fabrication procedures and for some operational conditions: Electric field stress, ESD = Electro-Static Discharge, or through TDDB as we saw before.*

## **MANUFACTURING DEFECTS 2(2)**

- ◆ Shorting/bridging defects.

- Shorts between signal/signal or signal/VDD or ground.

- Gate-Oxide Shorts (*as mentioned earlier*).

- Via punch-through, parasitic transistor leakage, defect pn junctions.

- Bridging defects getting more common below 28 nm.

- ◆ Open defects (opens are more difficult to detect in CMOS circuits).

- Missing conducting material or too much insulating material.

- Faults can be time-dependent: Narrow opens can allow for tunneling. Coupling capacitance interactions and leakage currents can make an open appear something else.

# Testing and debugging

# **THE WIDER MEANING OF TESTING AND DEBUGGING**

## ◆ Testing.

- Comprehensive and organized effort to exercise as many aspects as possible of an implementation for possible failure.

## ◆ Debugging.

- Upon discovery of failure(s) = bug(s), the comprehensive and organized effort to close the existing bugs of an implementation.

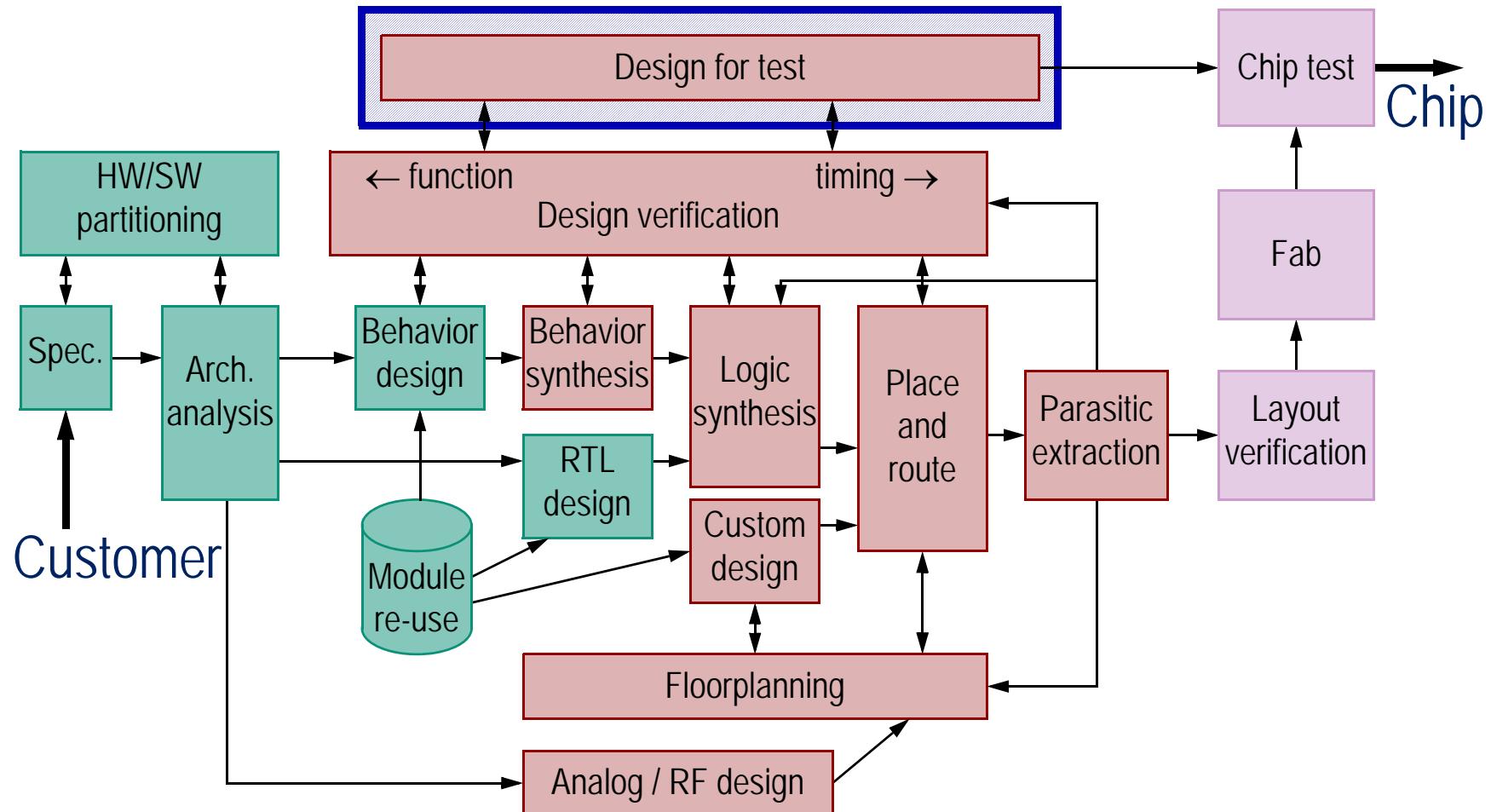

## **IMPLEMENTATION AND PRODUCTION FLOW**

- ◆ Design-for-test (DFT) considerations

(add dedicated test circuits).

- Find test vectors that can find physical defects in a short amount of time.

- ◆ Acceptance testing.

- Run pass/fail tests on manufactured chips.

- Run parametric tests for performance on manufactured chips.

- ◆ Failure analysis.

- Improve test coverage.

- Improve design for next iteration.

# **MANUFACTURING TESTS**

- ◆ In electronics often test refers to the physical, experimental procedure of evaluating the manufactured hardware using e.g. pattern generators and logic analyzers.

## TEST-VECTOR GENERATION

- ◆ In order to develop a test strategy, models of physical defects are needed: Fault models ...

- Stuck-at 0 fault, Stuck-at 1 fault, Bridging fault, etc.

- ◆ Fault simulation is used to find out how well a set of  $p$  test vectors can uncover defects in a circuit with  $n$  nodes.

- Perform logic simulation; inject one fault at a time:  $O(p n^2)$ .

- Fault simulation gives test vectors that have high test coverage.

- ◆ The automated process of finding efficient test vectors is called ATPG = Automatic Test Pattern Generation [D-algorithm, PODEM].

## **TESTING TERMINOLOGY 1(2)**

- ◆ A defect is an unintended difference between the implemented/fabricated hardware and its intended function.

- ◆ An error is an erroneous response by a defective system.

- ◆ A fault is a logic-level abstraction of a physical defect.

## **TESTING TERMINOLOGY 2(2)**

- ◆ Manufacturing tests (+ optional stress test).

- Check for defects after fabrication steps.

- Structural tests:

Function is irrelevant, signatures like in logic BIST work fine.

- ◆ Functional tests.

- Check and compare with desired (logic) functionality.

- ◆ Parametric tests.

- Check and compare with desired performance (speed, power, robustness, etc.).

- Scaling makes delay faults dominate physical defects (< 28nm).

## **TEST AND YIELD**

- ◆ For large, cutting-edge SoC/uP designs, very advanced IC processes are used.

- ◆ When a new IC process is introduced:

Manufacturing errors are more probable and the yield is low.

- Zero-yield test may happen for new chips.

- ◆ When the IC process has matured, yield has become high.

## **STRESS TEST**

- ◆ In a stress test, extreme operating conditions are used; using cycling over large intervals.

- In operating conditions, we include parameters such as temperature and mechanical stress.

- ◆ The stress test reveals how reliable a design is.

- Poor parts are breaking down and only the good parts are leaving the fab/foundry.

- Information on expected lifetime (Mean Time To Failure - MTTF) can be extracted.

## **THE BURN-IN TEST**

- ◆ Stress the chip by performing a burn-in procedure.

- Static burn-in: Put IC in oven. Remove from oven. Retest.

- Dynamic burn-in: Test at elevated temperatures...

- \* Chip should be packaged and a subset of I/Os used.

- \* Increase temperature to around 110°C.

- \* Increase supply voltage to around 30% above nominal value.

- NBTI for PMOSFETs may become a problem, and future ageing can accelerate.

- ◆ Now ... what happens if we happen to stress a chip, which has unusually low threshold voltages (due to variation)?

# **BURN-IN TEST CAN CAUSE THERMAL RUNAWAY**

Leakage increases in hot areas

⇒

Increased leakage heats the chip :-(

⇒

Heat can make hardware malfunction (or reduces Mean Time To Failure)

# **Design For Test (DFT)**

# PRESENT SCENARIO: DESIGN FOR TEST

## **ECONOMY OF ELECTRONICS**

### ◆ The cost of fixing an error.

- Fixing an error in initial design: cost ~ \$10.

- Fixing an error in layout: cost ~ \$1000 - \$500,000.

- Fixing an error when reaching volume production:

cost > \$100,000,000

(plus cost of replacing products = loss in precious goodwill).

### ◆ The cost of volume-oriented foundries/fabs.

- Cost for a fab ~ \$5,000,000,000 and rising!

## **DESIGN FOR TEST (DFT)**

- ◆ Test your manufactured design!

- Failing designs cost short term (replacement/repair) and long term (goodwill).

- Safety is a central issue in medical and vehicular equipment.

- ◆ Tests must be practical ⇒

Include hardware that enhances controllability and observability.

- ◆ Tests must be planned ⇒

A well-documented implementation makes test easier.

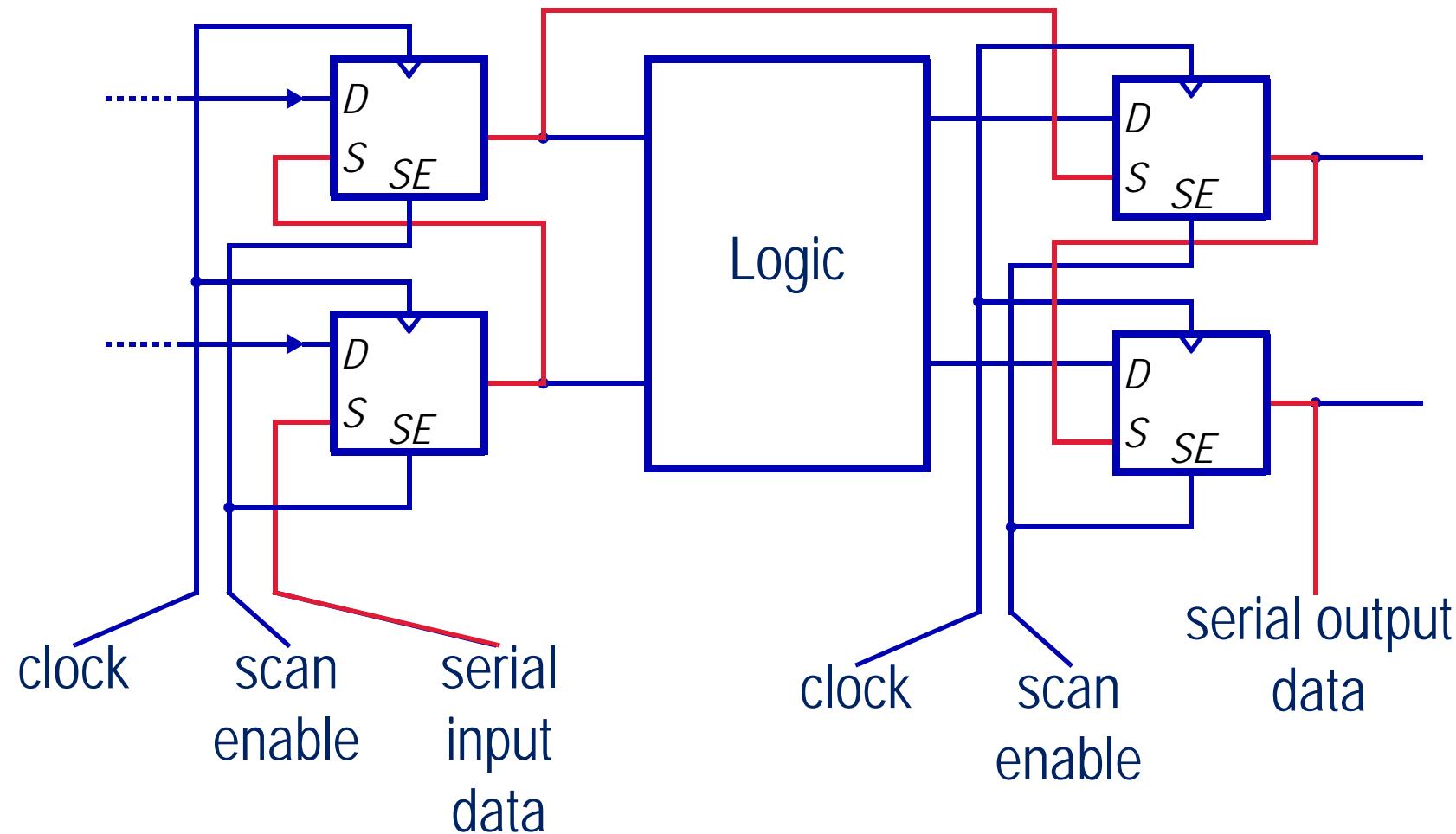

## **DFT TECHNIQUES**

- ◆ *Ad hoc* testing: for example, test point insertion for observation.

- ◆ Scan-based testing.

- Scan flip-flops connected in chains to allow test data to be moved in and out of logic core.

- ◆ Boundary scan - JTAG.

- ◆ Built In Self Test (BIST).

- Pattern generators + response analyzers built into the logic.

- Logic BIST (using scan chains).

- Memory BIST: Built-in self repair (1D or 2D) can replace defect memory cells with spare cells.

# PRINCIPLE OF SCAN CHAINS

## **EXTERNAL OR INTERNAL VECTOR GENERATION?**

- ◆ Traditionally scan chains are exercised using external ATPG-based automatic test equipment (ATE).

- ◆ To reduce test time, more I/O capacity is desired.

But test cost is dominated by ATE, whose cost depends on I/O capacity  $\Rightarrow$  What about internal tester?

- ◆ Logic BIST:

- Pseudo-random pattern generators (PRPG) generate vectors, which are applied to scan chains, whose outputs are combined in a multi-input signature register (MISR).

## **IMPLEMENTATION ASPECTS**

- ◆ ATPG: Specific faults + high test coverage + manufacturing tests.

- needs vector decompression/compression to be scalable (since I/O capacity does not increase fast enough).

- ◆ Logic BIST: Fault agnostic + lower coverage + more suitable for system tests, power-on tests, etc.

- ◆ Scan chain infrastructure significantly impacts implementation:

- Area overhead.

- Scan reordering: Ensure each chain sits inside one Clk/VDD domain. Check potential hold time problems.

- I/O pin count an issue. Pin sharing for logic and scan.

## **OTHER CHALLENGES WITH ATPG-BASED ATE**

- ◆ Scan tests using ATPG-based ATE exercise registers more than regular operation does. Continuous at-speed testing not possible due to excessive power.

- Use slow scan!

- But slow scan means less vectors are tested per time unit.

- ◆ Even for slow scan, simultaneous switching ( $di/dt$ ) is a problem.

- Use vectors with less switching activity  $\Rightarrow$  extends test vector space by ~30%.

- ◆ At-speed testing using ATPG ATE is possible; use short bursts to reveal critical timing.

## **OTHER CHALLENGES WITH BIST**

- ◆ Due to the pseudo-random generation, BIST cannot as easily as external ATPG target specific faults.

- Watch out for correlations:

Choice of PRPG and seeds is important.

## **EDA TOOLS FOR DFT**

- ◆ Siemens/Mentor.

- acquired LogicVision.

- offers Tessent Framework.

- ◆ Cadence.

- Modus Test Solution.

- ◆ Synopsys DFT.

- DFTMAX and TetraMAX.

- ◆ SynTest Technologies.

- RobustScan and TurboBIST-Logic.

## **RELIABILITY AND TEST: CONCLUSION**

- ◆ Our hardware platform is getting less reliable.

- IC device scaling is causing some reliability problems.

- Changing operating conditions are causing other problems.

- In total, a growing number of mechanisms have to be considered.

- ◆ Bottomline: We must test our electronic systems thoroughly!

- ◆ And to test our manufactured systems efficiently, we need to consider this test early, already during design / implementation.

- ◆ ATPG-based ATE vs logic BIST: Each has its role, strengths and weaknesses... but there is still a debate on which is "best".